# Design and Comparative analysis of processors based on Harvard and von Neumann architectures

# T. Bhanu Prakash Reddy<sup>1</sup>, M. Sundeep Roy<sup>2</sup>

<sup>1,2</sup>Student, Dept of ECE, Velagapudi Ramakrishna Siddhartha Engineering College, Vijayawada, India.

\*\*\*

**Abstract** - Computers became a part of our life. The brain behind these computers is a processor. Harvard and von Neumann architectures are the mostly used architectures for designing processors. In this paper simple processors using Harvard and von Neumann architectures are designed and are briefly compared. These processors are Reduced Instruction Set Computers (RISC), meaning the ISA (Instruction Set Architecture) is simple and optimized.

Key Words: CPU, Verilog, architecture, RISC, modelsim.

# 1. INTRODUCTION

We cannot imagine performing daily tasks without involving computers. In this era of IT, computers became a crucial part as many manually tasks are now automated. Importance of computers increased because of their ability to accomplish complex tasks accurately. Actual computation required to perform these tasks are done by the Central Processing Unit (CPU) of the computer. CPU is the unit that executes instructions of a program. Generally, all processors follow fetch, decode and execute steps. If one instruction is executed then the whole process is repeated for the following instruction. It is no wonder CPU is considered as the brain of the computer. There are two main architectures used for designing the processors:

- i. Von Neumann architecture

- ii. Harvard architecture.

In this work we proposed design of two 8-bit Reduced Instruction Set Computer (RISC) processors one using Harvard and another using Von-Neumann architectures. RISC stands for Reduced Instruction Set Computer. In these types of computers, the instruction set is highly optimized. Unlike Complex Instruction Set Computer (CISC), the instruction set of RISCs has only few basic steps, so it makes the hardware simpler to design.

# 2. HARVARD AND VON-NEUMANN ARCHITECTURES

Basically, there are two types of Computers:

a.) Fixed Program Computers – Their function is very specific and they couldn't be programmed. First computers had fixed

programs. Few simple computers still use this design. For example, a calculator is a fixed program computer.

b.) Stored Program Computers – These can be programmed to carry out many different tasks, applications are stored on them, hence the name. They have an instruction set and memory to store instructions, and computation is done according to that stored program.

Both von Neumann and Harvard architectures are for Stored Program Computers.

#### i. VON NEUMANN ARCHITECTURE:

Von Neumann architecture is first introduced by John von Neumann and others in First Draft of a Report on the EDVAC. It was published in 1945. In that document, Von Neumann described a design of a very high speed automatic digital computing system. The document is further subdivided into: a central arithmetic part, a central control part, memory, input, output, and external memory. Processors based on this architectures store data and instructions in the same memory. Since the bus is common for program data and instructions, data operation and instruction fetch cannot happen simultaneously. This type of storing results in a problem called von Neumann bottleneck. Because of this, the data transfer rate between CPU and memory is limited.

Fig.1 Von Neumann architecture block diagram

#### ii. HARVARD ARCHITECTURE:

Harvard architecture have separate memories and buses for instructions and program data. So, CPU can read an instruction and read/write data at the same time. Harvard architecture came into picture to eliminate the bottleneck problem in von Neumann architecture. The name Harvard is taken from a relay-based computer Harvard Mark I. For a given circuit complexity, Harvard architecture can be faster than von Neumann since it has separate paths to instructions and data.

Fig2. Harvard architecture block diagram

#### 3. PROPOSED MODELS

To avoid complexity in comparison of processors, same modules are used in designing both processors. The processors are modeled using Verilog HDL and simulated using the Modelsim tool. The ISA for proposed models is as shown in table1.

#### Table1. Instruction Set Architecture

| Instruction | M-format | ALU<br>src | ALU<br>Control | Branch | Jump | MemtoReg | MemWrite | RegWrite |

|-------------|----------|------------|----------------|--------|------|----------|----------|----------|

| add         | 0        | 0          | 00             | 0      | 0    | 0        | 0        | 1        |

| addi        | 0        | 1          | 00             | 0      | 0    | 0        | 0        | 1        |

| SW          | 0        | 1          | 00             | 0      | 0    | Х        | 1        | 0        |

| lw          | 0        | 1          | 00             | 0      | 0    | 1        | 0        | 1        |

| beq         | 0        | 0          | 01             | 1      | 0    | Х        | 0        | 0        |

| slti        | 0        | 1          | 10             | 0      | 0    | 0        | 0        | 1        |

| li          | 1        | 1          | 11             | 0      | 0    | 0        | 0        | 1        |

| j           | Х        | Х          | Х              | Х      | 1    | Х        | 0        | 0        |

# i. PROCESSOR IMPLEMENTED USING HARVARD ARCHITECTURE

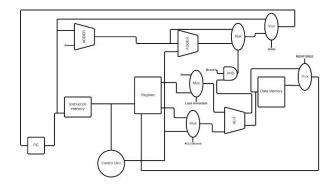

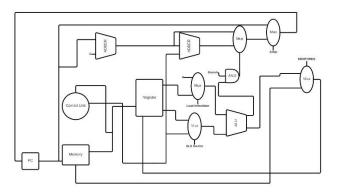

The main modules of Harvard design are Control unit, ALU, Register Unit, Program counter unit, Instruction memory and Data memory unit. The top-level schematic is as shown in fig3.

Fig3. Schematic diagram of Harvard processor

#### A. CONTROL UNIT

Control unit is a part of CPU that directs the operation of the processor. The simulation result of this module is as shown in fig4.

Fig4. Control unit simulation result

#### B. ARITHMETIC LOGIC UNIT

ALU is a part of CPU that carry out arithmetic and logic operations. The simulation result of this module is as shown in fig5.

| + 🌛 /ALU/ALUantri            | 2h1         | Zh0   | [2h1  | [2h2 | 2h3   |        | 2h0  |       | 2h1    |

|------------------------------|-------------|-------|-------|------|-------|--------|------|-------|--------|

| 🖬 🌛 /ALU/inputA              | 8'hff       | 81101 |       |      |       | (8'hff |      |       |        |

| 🖬 🅠 /ALU/inputB              | 8'hff       | 81102 |       |      |       |        |      | 8hff  |        |

| ■-4 /ALU/ALUOut<br>/ALU/Zero | 8h00<br>1h1 | 8h03  | [8hff | 801  | (8h20 |        | 8h01 | .8hfe | (3'h00 |

Fig5. ALU simulation result

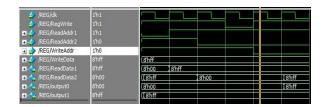

#### C. REGISTER UNIT

Register unit has registers that can e quickly accessible to CPU. The simulation result of this module is as shown in fig6.

Fig6. Register unit simulation result

# D. PROGRAM COUNTER UNIT

Program counter acts as instruction pointer. It holds the address of next instruction to be executed. The simulation result of this module is as shown in fig7.

| <b>1</b>                |            |       |      |         |       |       |

|-------------------------|------------|-------|------|---------|-------|-------|

| /getNextPC/PCSrc        | ihi<br>ihi |       |      |         |       |       |

| 🛃 /getNextPC/databus    | 8h03       | 8'h03 |      |         |       |       |

| 🖬 🥠 (get) lextPC/offset | 8h05       | 3'h00 |      |         | [8h05 |       |

| 🗄 🌛 /getWextPC/currPC   | 8h05       | 8'h01 | 8h02 | 8'h04   |       | [8h05 |

| E-🕹 /getNextPC/out      | 81603      | 8'h02 | 8h03 | 8h05    | Sh0a  | [8h03 |

|                         |            |       |      | 22.<br> |       |       |

Fig7. Program Counter simulation result

International Research Journal of Engineering and Technology (IRJET)e-ISSN: 2395-0056Volume: 08 Issue: 02 | Feb 2021www.irjet.netp-ISSN: 2395-0072

#### E. INSTRUCTION MEMORY

Instruction memory contains instructions. This memory does not have write signals. It only has read signals. The simulation result of this module is as shown in fig8.

| 🗉 🎝 /IM/iABUS    | -No Data- | (8'h00       | 8'h02       | 8'h03       | 8'h01     |

|------------------|-----------|--------------|-------------|-------------|-----------|

| 😐 🕁 /IM/iDATABUS | -No Data- | (8'h00       | 8'h22       | 8'h43       | 8'h01     |

| 🖅 🚽 /IM/ram      | -No Data- | (8'h00 8'h01 | 8'h22 8'h43 | 8'h84 8'h05 | 8'hfe 8'h |

|                  |           |              | 01122 01145 | 0110-01105  | 01112 011 |

Fig8. Instruction memory simulation result

#### F. DATA MEMORY

In data memory you can read and write values. The simulation result of this module is as shown in fig9.

Fig9. Data memory simulation result

- G. CPU

- The simulation result of overall CPU is as shown in fig10.

| <b>1</b> •               |     |      |       |       |        |        |       |       |  |

|--------------------------|-----|------|-------|-------|--------|--------|-------|-------|--|

| 🗳 (test_bench/dock       | 151 |      |       |       |        |        |       |       |  |

| 🍐 hist berchidk          |     |      |       |       |        |        |       |       |  |

| 🇳 Jast_bendhjaar         |     |      |       |       |        |        |       |       |  |

| 👍 Asst, bench, Regilinte |     |      |       |       |        |        |       |       |  |

| 👍 (test_bench/Pentilinta |     |      |       |       |        |        |       |       |  |

| 👍 (last_bench/Hemiliaad  |     |      |       |       |        |        |       |       |  |

| 👍 Jast Jendybranch       |     |      |       |       |        |        |       |       |  |

| 👍 (hist_bend)/PCS        |     |      |       |       |        |        |       |       |  |

| 🛀 Ast Jerd Auch          |     | 643  | 120   |       |        | 251    | 20    | 122   |  |

| 4 itest bench/           |     |      |       |       |        |        |       |       |  |

| 🖌 Aust, berdyktation     |     | 3101 | 19:02 | 18103 | (8704  | 187129 | 8108  | [Shab |  |

| 🛃 Nest bench in 48.15    |     | 3102 | 18201 | 18902 | (8703  | (82)4  | 8109  | 8108  |  |

| 👍 (heit, berch (n04748LS |     | 3107 | 18101 | 18122 | (\$143 | 28/184 | 8:50  | 15/40 |  |

| Anst herch RepAirteAddr  |     |      |       |       |        |        |       |       |  |

| Ast berch Addata1        |     | 3107 |       | 18901 | (#100  |        |       |       |  |

| 🔸 Anst bendy Followa 2   |     | 3101 |       | 15101 | Cathoo |        |       |       |  |

| Ast bench/WCeta          |     | 3102 | 18:01 | 18500 |        |        | 8:50  |       |  |

| 📣 (hist bench(cuti)      |     | 310: |       | 15101 | Cahoo  |        | -     |       |  |

| Ast berchiouts           |     | 3101 |       | _     | _      | _      | _     | _     |  |

| 📣 Jast bench/ULIInpun1   |     | 3103 |       | 15501 | (850   |        |       |       |  |

| test bench (ULI) roun2   |     | 3101 | 16-01 | 15102 | (8903  | 181:00 | 18:00 |       |  |

| Asst bench/ALUCUE        |     | 3102 | 18103 | 19403 | (1703  | 18700  | 8-00  |       |  |

| 👍 jast benchjüero        |     | -    |       |       |        |        |       |       |  |

| And berduktutatis        |     | 3101 |       |       |        |        |       |       |  |

| Anst bench/CacheSsap     |     |      |       |       |        |        |       |       |  |

| Ant bench // entoCache   |     | 3103 |       |       |        |        |       |       |  |

| 🔥 Nest Jench (Extended)  |     | 3101 | 18/01 | 8802  | (8003  | (8h04  | 8100  |       |  |

Fig10. CPU simulation result

#### ii. PROCESSOR IMPLEMENTED USING VON-NEUMANN ARCHITECTURE

The main modules of Von-Neumann design are Control unit, ALU, Register Unit, Program counter unit and Memory unit. The Control unit, ALU, Register Unit and Program counter unit used in this design is same as those modules used in Harvard design. The only difference between modules of these two designs is that the Harvard has two memory modules – one for instruction and other for data, whereas von Neumann design has a single memory module. The toplevel schematic diagram of this processor is as shown in fig11.

Fig11. Schematic diagram of von Neumann processor

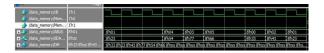

#### A. MEMORY UNIT

Unlike Harvard architecture, von Neumann has single memory section. This memory is used for bot instructions and data, The simulation result of this memory module is as shown in fig12.

| ∎/ram(data    | 8h11  | 8 | 11   |       |       |       |       |      |       |

|---------------|-------|---|------|-------|-------|-------|-------|------|-------|

| 🕞 🌛 /ram/addr | 8'h00 | 8 | 01   | 18101 |       | 3'h06 |       | 8h09 |       |

| 🌛 /łan/we     | 1h0   |   |      |       |       |       |       |      |       |

| 🌛 franjišk    |       |   |      |       |       |       |       |      |       |

| 🖬 📣 /ram/q    |       |   | 8he0 |       | (8h00 |       | 8/h02 |      | 18h00 |

Fig12. Memory unit simulation result

#### B. CPU

The overall simulation result of this CPU based on von Neumann architecture is as shown in fig13.

| <b>\$1</b> +        |      |       |        |        |        |        |       |                                       |

|---------------------|------|-------|--------|--------|--------|--------|-------|---------------------------------------|

| 👍 /pu_var\tlack     | thi  |       |        |        |        |        |       |                                       |

| 📣 /tau_van/dk       |      |       |        |        |        |        |       |                                       |

|                     |      |       |        |        |        |        |       |                                       |

|                     |      | -     |        | 1      |        |        |       |                                       |

| 🖕 /cou_von/MenWinte |      |       |        |        | Ť.     |        |       |                                       |

|                     |      |       |        | Ŧ      |        |        |       |                                       |

| 🍐 /cou_von/branch   |      |       |        |        |        |        |       | <b>Γ</b>                              |

|                     |      |       |        |        |        |        |       |                                       |

| 🖬 📣 /cou_von/RLUCel |      | ZhS   | (2h)   |        |        | ) zh2  | (210  | )2h1 (                                |

|                     |      |       |        |        |        |        |       | ا كما كخل                             |

|                     |      |       | (810)  | 189.02 | jawa   | 8164   | (8105 | 3745                                  |

|                     |      | 8-1.5 | (81/22 | 131+13 | ) ando | )Shell | [8100 | 13h64 )                               |

|                     |      |       |        |        |        |        |       | i i i i i i i i i i i i i i i i i i i |

|                     |      |       | (8150  | 137-00 |        |        |       |                                       |

|                     |      |       |        | 31:00  |        |        |       | )                                     |

|                     |      |       | [8h00  |        | jishco |        | _     | )                                     |

|                     |      |       | (815)  | 131-00 |        |        |       |                                       |

|                     |      | 8160  | _      |        |        |        |       |                                       |

|                     |      | 850   |        |        |        |        |       | )                                     |

|                     |      |       | (8102  | 101:03 | ) 8960 |        |       | )                                     |

|                     |      | 8750  | (8h02  | 197403 | ) 8760 |        |       |                                       |

|                     |      |       |        |        | 1      |        |       | l P                                   |

| 🖪 🐴 /pu_von/MentoCa | Sho. | 840   |        |        |        |        |       |                                       |

Fig13. Von Neumann CPU simulation result

#### 4. CONCLUSION

This paper presented the design and comparison of two processors, one using Harvard and another using von Neumann architecture. All modules used in this work are verified through exhaustive simulations. Although there is no significant difference in the performance of these proposed 8-bit processors, the difference would be obvious in high performance applications.

#### REFERENCES

[1] Mishra, S. K., Sarwade, D. P. Review of Five Stage Pipelined Architecture of 8-Bit Pico Processor. 2014.

[2] Seung Pyo Jung, Jingzhe Xu, Donghoon Lee,Ju Sung Park,Kangjoo, Kim, Koon-shik Cho" Design & Verification of 16 Bit RISC Processor "International SoC Design Conference 2008.

[3] Ke, X., Kejia, Z., Qiang, L., & Hao, M. The Architecture Comparison and the VLSI Implementation of the 32-Bit Embedded RISC. 2003.

[4] Sil, A., et, Al. An Energy-Efficient 32-Bit Processor for Sensor Platform in 90nm Technology. 2012. University of Louisiana at Lafayette.

[5] https://github.com/ysharma1126/8-bit-processor

[6] Aneesh, R.; Jiju, K. "Design of FPGA based 8-bit RISC controller IP core using VHDL", India Conference (INDICON), 2012 Annual IEEE, On page(s): 427 – 432.