# A Comparative Study of Multilevel Inverter Topologies

## Aditay Vardhan Singh<sup>1</sup>, Ravi Shankar Singh<sup>2</sup>

<sup>1</sup>UG student, Department of Electrical Engineering, Poornima College of Engineering, Jaipur, Rajasthan, India <sup>2</sup>Assistant Professor, Department of Electrical Engineering, Poornima College of Engineering, Rajasthan, India \*\*\*

Т

Abstract— In current situation multilevel inverter becoming popular in the industry for high voltage and medium voltage application additionally inside the renewable energy fields. The input voltage can be acquired from dc battery, energy storage capacitors or any type of renewable energy sources. The various multilevel inverter topologies are, Diode clamped multilevel inverter, flying capacitor multilevel inverter, Cascaded H-bridge converter. The specific field of applications consist of its use as UPS, high voltage DC transmission, Variable Frequency Drives, in pumps, conveyors etc.

Keywords— cascaded H-bridge, diode clamped, flying capacitor multilevel inverter (FCMLI), Multilevel inverter (MLI) topology

#### **1. INTRODUCTION**

The power electronic device which has potential to convert the DC power into AC power is called as inverter. Initially the inverters were used to drive mostly the lightening load when the grid gets off. However, in recent time due to increased advancement in technology inverters are used in motor drives, UPS, power system utilization. In earlier days simplest two level inverter were used and produces the output with two different voltage levels but it has harmonic voltage and high switching losses causes losses are increase. So, to overcome the this problem certain solution takes place in existing inverter such that levels can be improved more than two so that pure sinusoidal waveform is produced at the output voltage and harmonics inside the output can be suppressed and percentage of losses may be decreased and this topology is named as multilevel inverter topology. The multilevel inverter topology concept has been introduced in the early 1975 with three level converters. It is possible to increase the power rating with high number of voltage levels in the inverter. This reduces the device rating in the inverter. A multilevel inverter generates a smooth sinusoidal waveform from numerous dc voltage levels as its input. Multi level inverters have become an interesting area in the industrial applications for high power and voltage ranges. It can be easily interfaced with renewable energy sources for various high power applications.

#### **2. MULTILEVEL INVERTER**

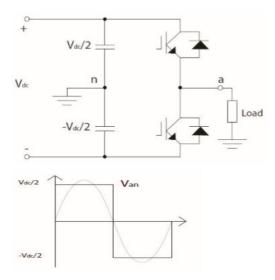

As in figure 1, Conventional two-level inverters normally generate an output AC voltage from an input DC voltage. Pulse Width Modulation switching scheme is used to generate the AC output voltage.

In the Multilevel Inverter topology (MLI), numerous DC voltage levels are added together to create a smoother output waveform. The acquired output waveforms have decrease harmonic distortions and dv/dt. The circuit design is more complicated with the increase in voltage levels due to addition of the valves. And complex control circuit is also required.

Fig-1:- Two level inverter and its output waveform without PWM

#### 3. COMPARISON BETWEEN CONVENTIONAL AND MULTILEVEL INVERTER

Table-1: Difference between conventional and multilevel inverter

| SI. |                              |                         |  |  |  |

|-----|------------------------------|-------------------------|--|--|--|

| No  | <b>Conventional Inverter</b> | Multilevel Inverter     |  |  |  |

|     | THD is high in the           | THD is Low in the       |  |  |  |

| 1   | output waveform              | output waveform         |  |  |  |

| 2   | High Switching stresses      | Low Switching stresses  |  |  |  |

| 3   | Not used for high            | Used for high voltage   |  |  |  |

|     | Voltage applications         | Applications            |  |  |  |

|     | High voltage levels          | High voltage levels can |  |  |  |

| 4   | cannot be produced           | be produced             |  |  |  |

| 5   | High dv/dt and EMI           | Low dv/dt and EMI       |  |  |  |

|     |                              | Lower switching         |  |  |  |

|     | High switching               | frequency, reduced      |  |  |  |

|     | frequency, increased         | switching losses        |  |  |  |

| 6   | switching losses             |                         |  |  |  |

#### 4. DIFFERENT MULTI LEVEL INVERTER TOPOLOGIES

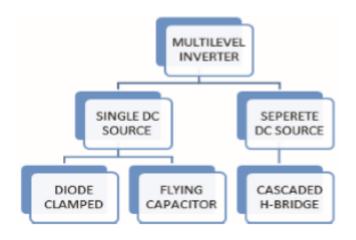

There are basically three types of multilevel inverter categorized according to the voltage source used in the inverter. The Fig.2 below indicates the topologies of multilevel inverter.

Fig-2: Classification of multilevel inverter

## 4.1 DIODE CLAMPED MULTILEVEL INVERTER

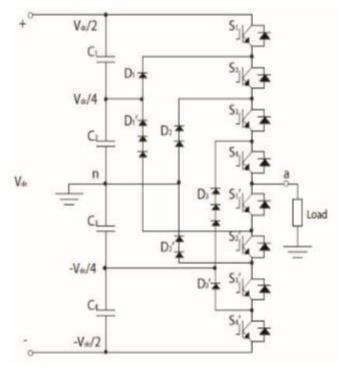

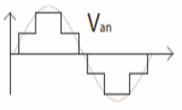

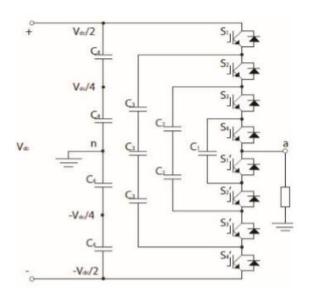

A five-level diode clamped inverter is shown in Fig. 2. The voltage of dc-bus is split into five levels by four capacitors connected in series C1, C2, C3 and C4. The center point between C1, C2 and C3, C4 defined as neutral point. The output voltage Van has five states: Vdc/4, Vdc/2, 0, -Vdc/4, and -Vdc/2.

Fig3: Single phase leg of a 5 level diode clamped inverter topology and its waveform

The fundamental elements that discriminate this circuit from a traditional inverter are D1, D1, D2, D2, D3 and D3. When voltage throughout a and 0 is Vdc, switch S1 to S4 are turned on. In this condition, D1 stabilize the voltage distribution between S1 to S4 with S1 blocking the voltage across C1, S2 blocking the voltage across C2, S3 blocking the voltage across C3 and S4 blocking the voltage across C4. The neutral point n is considered as the output phase voltage reference point to illustrate how the staircase voltage is included. Voltage level and the switching states are shown in Table I. The identical thing can be explained for seven and nine level diode clamped inverter also.

Table II: Five voltage levels and switching states

Fig-4: Simulation circuit of diode clamped multilevel inverter

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056

Volume: 05 Issue: 03 | Mar-2018

www.irjet.net

clamped inverter. No Clamping diodes are required in this inverter. The output voltage is simply half of the input DC

Fig-5: Output waveform of 5 level diode clamped MLI

#### **ADVANTAGES:**

IRIET

- Voltage across the switch is only half of the dc-link voltage.

- Entire phase share a common dc bus, which minimize the capacitance requirement of the converter

- Capacitance of the capacitor is low and they are recharged.

- Back to back inverters are used.

- Efficiency is high at fundamental frequency.

#### **DISADVANTAGES:**

- Diode clamped MLI have a practical limit on the number of levels, because it required clamping diode.

- If the control and monitoring are not precise, Dc level will discharge.

# **APPLICATIONS:**

- 1. Static VAR compensation

- 2. Variable speed motor drives

- 3. High voltage system interconnections

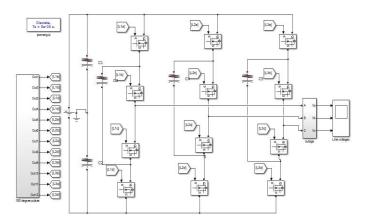

# 4.2 FLYING CAPACITOR MULTILEVEL INVERTER

The flying capacitor multilevel inverter is same as the diode clamped MLI only difference is that in place of clamping diodes capacitors are used for clamping purpose. This topology is having the tree structure of dc side capacitors where voltage of every capacitors differs from that of the next capacitor.

The voltage across every capacitor and switch is Vdc. An m level flying capacitor inverter needs Switches: (2m - 2) Number of capacitors: (m - 1)

The capacitor clamped switching cells are connected in series. The switching states are same as that of diode

voltage. A five level topology is shown below in figure 6.

Fig-6: Single phase of a 5-level Flying capacitor MLI

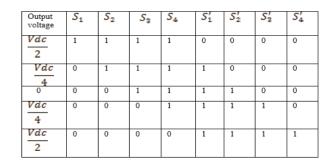

# **Table II** – Five voltage levels and switching states for<br/>flying capacitor

| Output<br>voltage | <i>S</i> <sub>1</sub> | <i>S</i> <sub>2</sub> | Sa | S <sub>4</sub> | <i>S</i> <sub>1</sub> ' | <i>S</i> <sub>2</sub> ' | <i>S</i> <sup>'</sup> <sub>3</sub> | <i>S</i> <sup>7</sup> <sub>4</sub> |

|-------------------|-----------------------|-----------------------|----|----------------|-------------------------|-------------------------|------------------------------------|------------------------------------|

| $\frac{Vdc}{2}$   | 1                     | 1                     | 1  | 1              | 0                       | 0                       | 0                                  | 0                                  |

| $\frac{Vdc}{4}$   | 0                     | 1                     | 1  | 1              | 1                       | 0                       | 0                                  | 0                                  |

| 0                 | 0                     | 0                     | 1  | 1              | 1                       | 1                       | 0                                  | 0                                  |

| $\frac{Vdc}{4}$   | 0                     | 0                     | 0  | 1              | 1                       | 1                       | 1                                  | 0                                  |

| $\frac{Vdc}{2}$   | 0                     | 0                     | 0  | 0              | 1                       | 1                       | 1                                  | 1                                  |

International Research Journal of Engineering and Technology (IRJET)

e-ISSN: 2395-0056 p-ISSN: 2395-0072

Volume: 05 Issue: 03 | Mar-2018

www.irjet.net

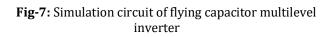

Fig-8: Output waveform of simulation circuit of flying capacitor MLI

#### **ADVANTAGES**:

IRIET

- Eliminates the clamping diode problems

- Phase redundancies are available for balancing the voltage levels of the capacitors, real and reactive power flow controlled

- The large number of capacitor enables the inverter to save from short duration outage and deep voltage sags

#### **DISADVANTAGES:**

- Complex start-up

- Lower Switching efficiency

- Capacitors are expensive than diodes

- Voltage control across all the capacitors is difficult

#### **APPLICATIONS:**

- 1. Induction motor control using DTC circuit

- 2. Static VAR generation

- 3. Both AC-DC and DC-AC conversion applications

- 4. Converters with Harmonic distortion capability

- 5. Sinusoidal current rectifiers

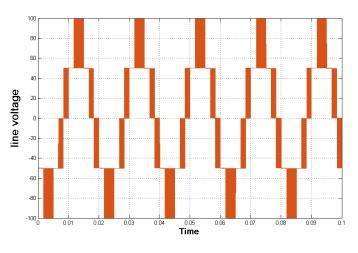

#### 4.3 CASCADED H-BRIDGE MULTILEVEL INVERTER

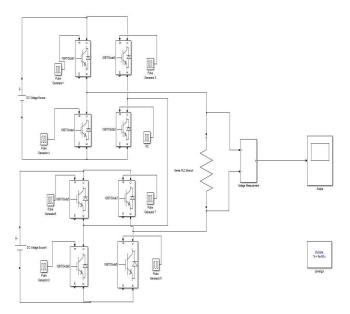

The general structure of the cascaded multilevel inverter for single phase is shown in figure 9. In Cascaded H-Bridge multilevel inverter, Number of H-Bridges are connected in series. Each H-Bridge having separate DC source which is to be obtained from any natural sources, ultra capacitors, fuel cells or batteries to produce inverted ac output [5].

The advantage of this method is any capacitor or diode is not required for clamping purpose and output waveform is like a sinusoidal in nature if number of level increases even we don't filter it.

Fig-9: Single phase cascaded h-bridge 5 level inverter

For a single phase 5 level cascaded H-Bridge multilevel inverter two H-Bridges are required. These two H-Bridge cells are connected in series which are fed by DC voltage sources. The output of two H Bridges is connected in series in such a way that the total output is the sum of all individual H-Bridge cell output [5]. Than the output voltage is,

Where,

V=Total output voltage.

Va=Output voltage of first H-Bridge cell. Vb=Output voltage of second H-Bridge cell

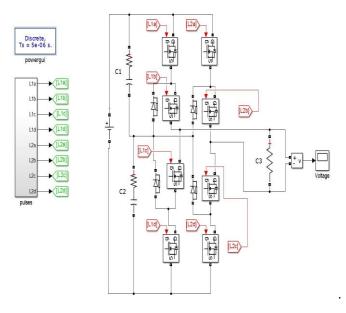

Fig-10: Simulation circuit of cascaded H- bridge 5 level inverter

International Research Journal of Engineering and Technology (IRJET)

e-ISSN: 2395-0056 p-ISSN: 2395-0072

Volume: 05 Issue: 03 | Mar-2018

www.irjet.net

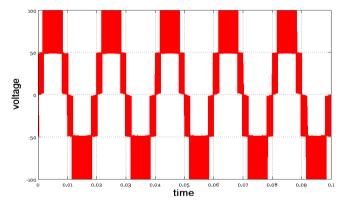

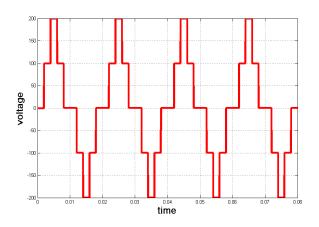

Fig-11: Output waveform of cascaded H bridge 5 level inverter

#### **ADVANTAGES:**

IRIET

- Total harmonic distortion is very low in the output waveform without any filter circuit

- Operates at both fundamental switching frequencies

- Easy packaging and storage

- Produce common mode voltage, stress is reduced

- Low distortions in the input current

### **DISADVANTAGES:**

- Separate DC sources or capacitor are required for each module But it is more suitable for photovoltaic application since each photovoltaic array can act as a separate DC source.

- Y- connected cascaded MLI are suited for STATCOM, power line conditioning but it can't be used for compensation & connecting unbalanced current

#### **APPLICATIONS:**

- 1. Motor drives

- 2. Electric vehicle drives

- 3. DC power source utilization

- 4. Power factor compensators

- 5. Back to back frequency link systems

- 6. Interfacing with renewable energy resources.

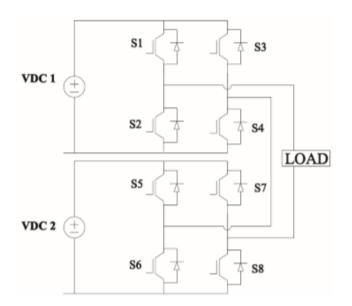

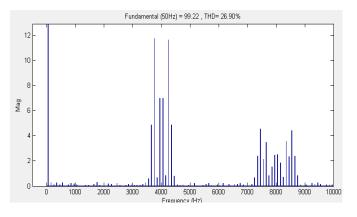

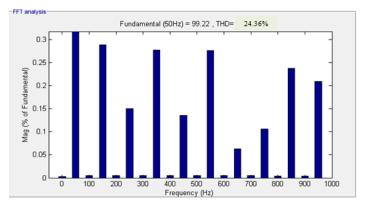

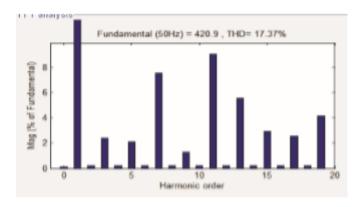

### **5. TOTAL HARMONIC DISTORTION ANALYSIS**

In different type of multilevel inverter the total harmonic distortion shows in below figure.

The THD level in diode clamped MLI is highest and in cascaded H-bridge MLI vary low. Therefore , the diode clamped MLI are most commonly used in low power application ,flying capacitor in medium power application and cascaded H-bridge used in high power application.

Fig-12: THD of 5 level diode clamped MLI

Fig-13: THD of 5 level flying capacitor MLI

#### 6. CONCLUSION

This paper present comparative study of various topologies of the multilevel inverter. The advantage, disadvantage and application of each topology are also discussed. The MLI has the ability to reduce total harmonic distortion (THD), Electromagnetic interference (EMI), Voltage stress on the switches and dv/dt problems. Based on the proposed study it can be concluded that the Cascaded H-bridge inverter is best among these three multilevel inverter. Research works are in progress considering the structure complexity and control circuits. Volume: 05 Issue: 03 | Mar-2018

www.irjet.net

#### REFERENCES

- [1] Anjali Krishna R. and Dr L Padma suresh "A brief review on multilevel inverter topologies" Conference on Circuit, Power and Computing Technologies [ICCPCT] 2016.

- [2] Addagatla Nagaraju and Akkela Krishnaveni "Modified Multilevel Inverter Topology with Minimum Number of Switches" IJSTE International Journal of Science Technology & Engineering volume 3 issue 09 March 2017

- [3] Amol K. Koshti and M.N. Rao "A Brief review on multilevel inverter topologies" 2017 International Conference on Data Management, Analytics and Innovation (ICDMAI),2017.

- [4] Mayuresh Dave "A Comparative Study of Photovoltaic (PV) based Diode Clamped Multilevel Inverter (DCMLI)" 2013.

- [5] Pravin T. Jadhav Swapnil Y.Gadgune, and Lohit R. Chaudhary "Implementation of Shunt APF based on Diode Clamped and Cascaded H-Bridge Multilevel Inverter" IEEE 2015.

- [6] Y. Sato, M. Kawasaki, and T. Ito "A Diode-Clamped Multilevel Inverter with Voltage Boost Function" 8th International Conference on Power Electronics -ECCE Asia May 30-June 3, 2011.

- [7] Zahra Malekjamshidi and Mohammad Jafari "A Comparative Study on Characteristics of Major Topologies of Voltage Source Multilevel Inverters" 2014 IEEE Innovative Smart Grid Technologies -Asia (ISGT ASIA) 2014.

- [8] P.Kobrel and J.Pavelka "Study Model of Flying Capacitors Multilevel Inverter" International Power Electronics and Motion Control Conference, EPE-PEMC 2012.

- [9] Fang Z. Peng, Wei Qian, and Dong Cao "Recent Advances in Multilevel Converter/Inverter Topologies and Applications" International Power Electronics Conference 2010.

- [10] Rekha Agarwal "A New Multilevel Inverter for Grid Connection of PV Modules" IEEE 2016.

- [11] Kamaldeep Boora and Jagdish Kumar "General topology for asymmetrical multilevel inverter with reduced number of switches" IET Power Electronics 2017.

- [12] M. Murugesan1et al. "different types of multilevel inverter topologies – a technical review" International Journal of Advanced Engineering Technology march 2016.

- [13] Gayathri Devi B. and M. Mahesh "A Brief Survey on Different Multilevel Inverter Topologies for Grid-Tied Solar Photo Voltaic System" 5th IEEE International Conference on Smart Energy Grid Engineering 2017

- [14] Ebrahim Babaei and seyed hossein "New cascaded multilevel topology with minimum number of switches" Elsevier june 2009

- [15] Niralkumar Rakholiya et al. "Multilevel Inverter Topology" –International Journal for Innovative Research in Science & Technology volume 3 issue 11 April 2017.