Volume: 05 Issue: 02 | Feb-2018

www.irjet.net

e-ISSN: 2395-0056 p-ISSN: 2395-0072

# A Comparative Study of Symmetrical and Asymmetrical Cascaded H Bridge Multilevel Inverter Topology for Industrial Drive

## Aparna Prayag<sup>1</sup>, Sanjay Bodkhe<sup>2</sup>

<sup>1</sup>Research Scholar, Electrical Engg. Department, G. H. Raisoni college of Engg, Nagpur, India <sup>2</sup> Former Professor, Electrical Engg. Department, G.H. Raisoni college of Engg, Nagpur, India

**Abstract** - *In recent years multilevel inverter technology* has become popular for medium and high power industrial applications. There are three main multilevel inverter topologies-Neutral Point Clamped, Flying Capacitor and Cascaded H Bridge. Cascaded H Bridge has become famous because of its modular design, simple control, reliability, availability and the absence of capacitor imbalance problem. *In this paper we are focusing on this topology which is series* connection of several H-Bridge cells with equal and un-equal magnitude of dc sources known as symmetrical and asymmetrical structure. Here symmetrical, binary asymmetrical and trinary asymmetrical topologies (formed by cascading two H-bridge cells) fed induction motor drives are compared in order to find an optimum arrangement with high quality output voltage. Performance of these structures is verified through computer simulation MATLAB/Simulink.

*Key Words*: Multilevel inverter, symmetrical, asymmetrical, Cascaded H Bridge, Total harmonic distortion (THD).

#### 1. INTRODUCTION

High performance a.c drive systems require high quality inverter output with low harmonic contents. Conventional two level inverters require high switching frequency to obtain a quality output voltage waveform. In high power and high voltage applications, these two level inverters, have some limitations in operating at high frequency. Harmonic reduction by raising switching frequency of two level inverter is difficult. From this aspect Multilevel (begins with three level) approach is promising alternative.

The main conception of multilevel inverter (MLI) is to achieve higher power by using number of power switches with several low voltage dc sources. It can produce output voltage waveform in steps which is closer to sine wave and reduces total harmonic distortion. Important points regarding topological structure of multilevel inverter are:

- It should have less switching devices as far as possible.

- It should be capable of enduring very high input voltage such as HVDC transmission for high power applications.

- Each switching device should have lower switching frequency owing to multilevel approach.

Recently multilevel inverters have been used in various industrial applications like distributed generation ,adjustable speed drives, flexible ac transmission system,, HVDC, electrical vehicles etc. due to noticeable advantages like high quality output voltage using low switching frequency, low harmonic contents, low electromagnetic interference, less voltage stress on power switches, more efficiency and low dv/dt stress on load [1]-[9].

Improvement in these advantages is possible by increasing number of levels of output voltage waveform but it requires large number of switches that makes circuit complex. It also raises cost and size of the circuit.

#### 2. CASCADED H-BRIDGE MULTILEVEL INVERTER

Cascaded H Bridge multilevel inverter is also known as multi-cell inverter. It consists of series connected H-bridges. In the topology each H-bridge is supplied by isolated dc source of identical value on its dc side and connected in series on their ac side. Batteries, fuel cells or ultra-capacitors are used as isolated dc sources [10]. The total output voltage is attained by adding voltages produced by each H-bridge connected to form cascaded circuit. Each cell creates three voltage levels positive, zero and negative by linking dc source to ac output through various arrangements of the four switches used in it.

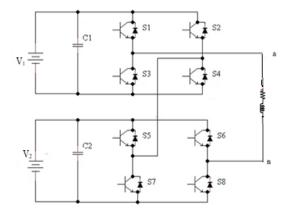

Fig.1 presents single phase structure of CHB-MLI using two H bridges. An output voltage waveform is obtained by summing the output voltage of both the cells connected in series.

Fig -1: Single phase leg of CHB

## International Research Journal of Engineering and Technology (IRJET)

Volume: 05 Issue: 02 | Feb-2018

www.irjet.net

For two H-bridge cascaded topology this structure generates

e-ISSN: 2395-0056

p-ISSN: 2395-0072

7 levels with maximum value 3Vdc.

If dc voltage sources are in the ratio of 1:3, then the inverter is known as trinary asymmetric multilevel inverter. The value of each dc source can be calculated as

$$V_k = 3^{(k-1)} V dc$$

$k = 1, 2, \dots, m.$  (8)

In this case number of voltage levels and maximum voltage generated can be calculated as

$$n = 3^m$$

$$V_M = \frac{(3^m - 1)}{2} V dc$$

(10)

Now, for two H-bridge cascaded topology this structure generates 9 levels with maximum voltage 4Vdc.

All these points of asymmetrical inverter are summarized in table 1.

| Binary Asymmetric CHB-<br>MLI                                          | Trinary Asymmetric CHB-<br>MLI                                         |

|------------------------------------------------------------------------|------------------------------------------------------------------------|

| Voltage sources are in the ratio 1:2                                   | Voltage sources are in the ratio 1:3                                   |

| Value of dc voltage source $V_k = 3^{(k-1)} V dc$ $k = 1, 2, \dots m.$ | Value of dc voltage source $V_k = 3^{(k-1)} V dc$ $k = 1, 2, \dots m.$ |

| No. of output voltage levels $n = 2^{(m+1)} - 1$                       | No. of output voltage levels $n = 3^{m}$                               |

| Maximum voltage generated. $V_M = (2^m - 1)Vdc$                        | Maximum voltage generated. $V_M = \frac{(3^m - 1)}{2} Vdc$             |

# 3. COMPARISON BETWEEN SYMMERICAL AND ASYMMERICAL CASCADED H BRIDGE MULTILEVEL INVERTER

From above discussion it is seen that trirnary asymmetrical multilevel inverter can produce more voltage levels and higher maximum output voltage with the same number of bridges as compared to symmetrical and binary asymmetrical structure. Table 2 presents comparison based on the number of levels (n), number of switches (Ns), dc sources (Nd) maximum output voltages ( $V_M$ ) and number of variety in voltage magnitudes (Nv), total voltage blocked by switches ( $V_b$ ) when m number of cells are connected in series.

If m numbers of H-bridges are joined in series then total voltage across the load is

$$(V_{an}) = (V_O)_1 + (V_O)_2 + \dots + (V_O)_m$$

$$(V_{an}) = \sum_{k=1}^m (V_O)_m$$

(1)

#### 2.1 Symmetrical Cascaded H-Bridge Inverter

When each cell of CHB-MLI is supplied by same magnitude of dc source then this structure is known as symmetrical structure.

The magnitude of dc source is given as

$$V_k = Vdc$$

$$k = 1, 2, \dots m.$$

(2)

$$V_1 = V_2 = .... = V_m = Vdc$$

The total number of output voltage levels n in symmetric multilevel inverter is given by

$$n = 2m + 1 \tag{3}$$

Where n is number of power cells used for cascade structure The maximum voltage generated by this arrangement is

$$V_M = m \times Vdc \tag{4}$$

For instance, if m=2 as shown in Fig. 1 it generates 5 level voltage with maximum voltage 2Vdc.

#### 2.2 Asymmetrical Cascaded H-Bridge Inverter

Asymmetrical multilevel inverters help to produce more number of output levels without increasing the number of cells. The magnitude of dc voltages sources can be selected according to a geometric progression with a factor of 2 or 3 [11].

If dc voltage sources are in the ratio of 1:2, then the inverter is known as binary asymmetric multilevel inverter. The value of each dc source can be calculated as

$$V_k = 2^{(k-1)} V dc k = 1, 2, \dots, m.$$

(5)

The effective number of output voltage levels n and maximum voltage generated can be expressed as

$$n = 2^{(m+1)} - 1 \tag{6}$$

$$V_M = (2^m - 1)Vdc \tag{7}$$

## International Research Journal of Engineering and Technology (IRJET)

Volume: 05 Issue: 02 | Feb-2018

www.irjet.net

**Table -2:** Comparison of Symmetrical and Asymmetrical CHB-MLI

| Parameters | Symmetrical | Asymmetric            | cal Structure           |

|------------|-------------|-----------------------|-------------------------|

|            | Structure   | Binary                | Trinary                 |

| n          | 2m + 1      | 2 <sup>(m+1)</sup> -1 | 3 <sup>m</sup>          |

| Ns         | 4 <i>m</i>  | 4 <i>m</i>            | 4 <i>m</i>              |

| Nd         | m           | m                     | m                       |

| $V_M$      | mVdc        | $(2^m - 1)Vdc$        | $\frac{(3^m-1)}{2}Vdc$  |

| Nv         | 1           | m                     | m                       |

| $V_b$      | 4mVdc       | $4(2^m-1)Vdc$         | 2(3 <sup>m</sup> -1)Vdc |

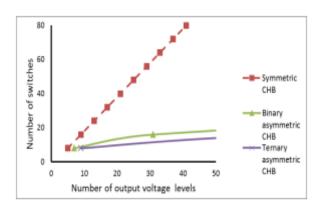

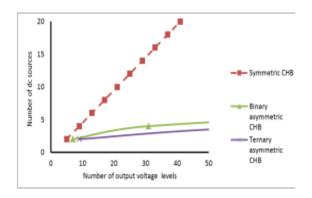

Chart 1 compares number of switches required to generate specific number of output voltage levels and Chart 2 shows number of dc sources required for the three configurations. It is clear that trinary asymmetrical configuration needs less components

**Chart -1**: Number of switches vs number of output voltage levels

**Chart -2**: Number of dc sources vs number of output voltage levels

#### 4. SIMULATION STUDY

The three phase symmetrical, binary asymmetrical and trinary asymmetrical cascaded H-bridge multilevel inverters fed three phase induction motor are modelled in MATLAB/Simulink environment. In each model configuration

two H -bridges are used, so that number of switches and number of dc sources in all the models are same. The switches used in the simulations are assumed to be ideal. Separate dc sources are used in the simulation studies. In practice these dc voltage sources are available via distributed energy resources like photovoltaic panels, fuel cells and ultracapacitors. If the available source is an ac source then the required dc voltage sources can be obtained by using rectifiers.

e-ISSN: 2395-0056

p-ISSN: 2395-0072

A multicarrier level shifted phase disposition PWM scheme is used in this paper to generate pulses for the switches of CHB-MLI. The conventional sinusoidal PWM technique can be applied to multilevel inverter topologies by using multiple carriers. Therefore it is known as multi-carrier PWM technique. A sinusoidal reference waveform of fundamental frequency is compared with high frequency carrier waveforms having same amplitude. For *m* level inverter (*m*-1) carriers are required [12].

Simulation parameters used are given in Table 3 and results are shown from Fig. 2 to Fig.16. Comparison is given in Table 4

**Table -3:** Simulation Parameters

| Description                         | Parameter     | Value       |

|-------------------------------------|---------------|-------------|

| Symmetric inverter                  | V1            | 160.5 volts |

|                                     | V2            | 160.5 volts |

| Binary asymmetric inverter          | V1            | 214 volts   |

|                                     | V2            | 107 volts   |

| Trinary asymmetric inverter         | V1            | 180 volts   |

|                                     | V2            | 60 volts    |

| Load-<br>3 Phase Induction<br>Motor | Rated voltage | 400 volt    |

|                                     | Rated current | 10 amp      |

|                                     | Rated power   | 5.4 H.P     |

|                                     | Rated speed   | 1430 rpm    |

|                                     | Rated torque  | 2.9 N-m     |

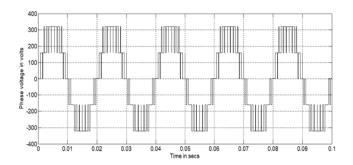

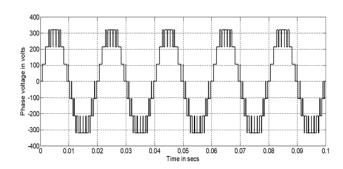

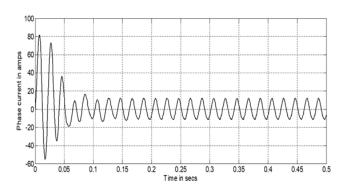

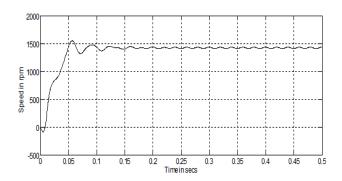

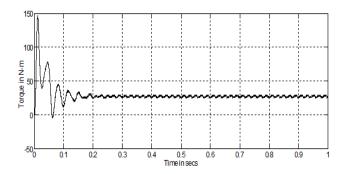

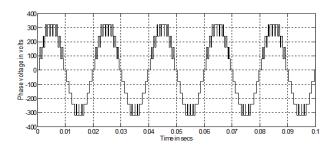

# 4.1 Simulation Results Of Symmetric CHB 5-Level Inverter

Fig -2: Phase Voltage (V<sub>A</sub>) Waveform

© 2018, IRJET

www.irjet.net

e-ISSN: 2395-0056 p-ISSN: 2395-0072

Volume: 05 Issue: 02 | Feb-2018

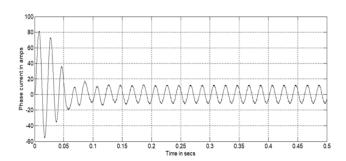

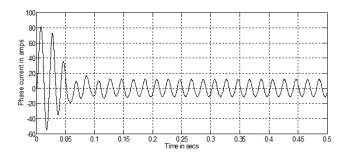

Fig -3: Phase Current (IA) Waveform

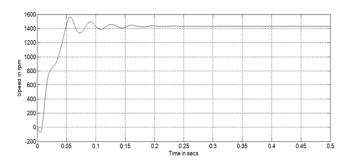

Fig -4: Rotor Speed

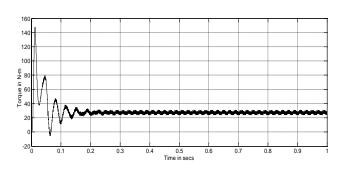

Fig -5: Electromagnetic Torque

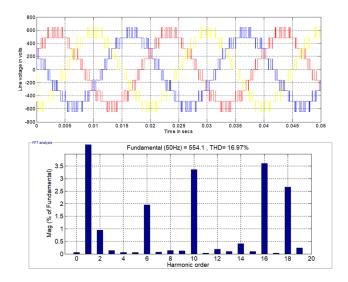

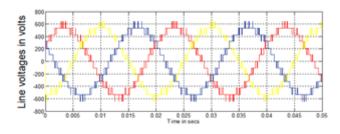

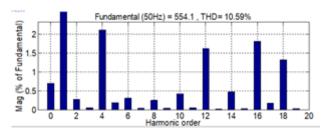

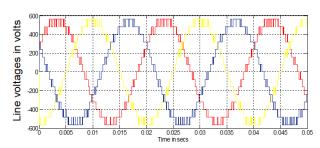

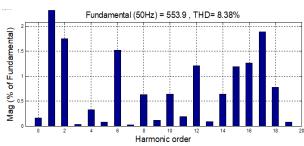

Fig -6: Line voltages and Harmonic Spectrum of Voltage  $$V_{AB}$$

# **4.2 Simulation Results Of Binary Asymmetric CHB 7-Level Inverter**

Fig -7: Phase Voltage (V<sub>A</sub>) Waveform

Fig -8: Phase Current (I<sub>A</sub>) Waveform

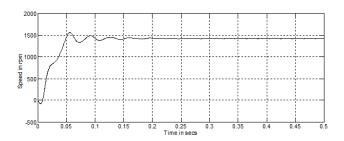

Fig -9: Rotor Speed

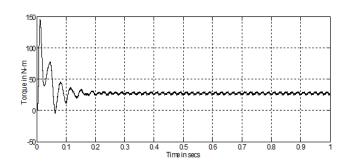

Fig -10: Electromagnetic Torque

www.irjet.net

p-ISSN: 2395-0072

e-ISSN: 2395-0056

Volume: 05 Issue: 02 | Feb-2018

Fig -11: Line voltages and Harmonic Spectrum of Voltage

#### 4.3 Simulation Results Of Trinary Asymmetric **CHB 9-Level Inverter**

Fig -12: Phase Voltage (V<sub>A</sub>) Waveform

Fig -13: Phase Current (I<sub>A</sub>) Waveform

Fig -14: Rotor Speed

Fig -15: Electromagnetic Torque

Fig -16: Line voltages and Harmonic Spectrum of Voltage  $V_{AB}$

**Table -4:** Comparison of Performance Parameters of Symmetric and Asymmetric CHB Inverter

| Parameters Symmetric inverter | Symmetric | Asymmetric inverter      |                           |

|-------------------------------|-----------|--------------------------|---------------------------|

|                               |           | Binary<br>asymmetr<br>ic | Trinary<br>asymmetri<br>c |

| Number of dc sources          | 2         | 2                        | 2                         |

| Number of switches            | 8         | 8                        | 8                         |

| Fundamenta<br>l Frequency     | 50 Hz     | 50 Hz                    | 50 Hz                     |

| Carrier<br>frequency          | 1 kHz     | 1 kHz                    | 1 kHz                     |

| Voltage<br>levels             | 5         | 7                        | 9                         |

| VL (volts)                    | 554.1     | 554.1                    | 553.9                     |

| Voltage THD<br>(%)            | 16.97     | 10.59                    | 8.38                      |

#### International Research Journal of Engineering and Technology (IRJET)

#### 5. CONCLUSIONS

In this paper the comparison of symmetrical, binary asymmetrical and trinary asymmetrical CHB-MLI with two H-bridges in series fed induction motor is carried out. MATLAB/Simulink models are developed for all the three topologies. Using PD-PWM a pulse generation circuit is designed.

From simulation results it is observed that the generated voltage spectrum is very much improved for nine level inverter topology. Among three configurations trinary- CHB inverter requires least number of switches and dc sources and generates high quality voltage with minimum harmonics.

Using this configuration motor performance is better. It is clear from simulation waveform that the output current waveform is smoother. The currents fluctuate up to 0.1 sec and after that it reaches a constant value. The extreme high value of current at the starting points of the simulation is due to the fact that before the rotor gains any speed, the stator acts as a very high power load. The fluctuations in the current values die out at about 0.15 sec and the currents attain a fairly constant value to reach its full speed of 1430 rpm.

The electromagnetic torque characteristic of the induction motor supplied by three phase asymmetrical nine level inverter shows that at the starting instant, the torque has an oscillating characteristic. A nearly constant electromagnetic torque is obtained after a time of 0.15 sec.

It is observed that as the stator currents settle to a constant value the electromagnetic torque also attains a fairly constant value. Torque achieves a mean value of about 26.9 N-m at steady state

CHB inverter requires least number of switches and dc sources and generates high quality voltage with minimum harmonics.

#### REFERENCES

- [1] J. Rodriguez, J-S. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls, and applications," IEEE Trans. Industrial Electronics, Vol. 49, No. 4, pp.724-738, Aug. 2002.

- [2] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, and M. A. M. Prats, "The age of multilevel converters arrives," IEEE Industrial Electronics Mag., Vol. 2, No. 2, pp. 28-39, Jun. 2008.

- [3] L. M. Tolbert, F. Z. Peng, and T. G. Habetler, "Multilevel converters for large electric drives," IEEE Trans. Ind. Appl., Vol. 35, No. 1, pp. 36-44, Jan./Feb. 1999.

[4] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Pérez, "A survey on cascaded multilevel inverters," IEEE Trans. Ind. Electron., vol. 57,no. 7, pp. 2197–2206, Jul. 2010.

e-ISSN: 2395-0056

- [5] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. Franquelo, B. Wu,J. Rodriguez, M. Perez, and J. Leon, "Recent advances and industrial applications of multilevel converters," IEEE Trans. Ind. Electron., vol. 57,no. 8, pp. 2553–2580, Aug. 2010.

- [6] H. Abu-Rub, J. Holtz, and J. Rodriguez, "Medium-voltage multilevel converters–State of the art, challenges, and requirements in industrial applications," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2581–2596, Aug. 2010

- [7] A.Nabae, I. Takahashi, H.Akagi, "A new neutral-point clamped PWM inverter," IEEE Trans. Ind. App. vol. IA-17, No.5, pp 518-52, Sept/Oct. 1981.

- [8] T. A. Meynard, H. Foch, "Multilevel conversion: High voltage choppers and voltage source inverters," IEEE-PESC Conference Record, pp.397-403,1992.

- [9] F. Z. Peng and J. S. Lai, "Multilevel cascade voltage-source inverter with separate DC source," U.S. Patent 5 642 275, June 24, 1997.

- [10] Farid Khoucha et al," A comparison of symmetrical and asymmetrical three-phase H-bridge multilevel inverter for DTC induction motor drives," IEEE Trans. on Energy Conversion, vol.. 26, no. 1, Mar.2011

- [11] Juan Dixon, Javier Pereda "Asymmetrical multilevel inverter for traction drives using only one dc supply" IEEE Trans. On Vehicular Technology, vol. 59, no. 8, October 2010.

- [12] Brendan Peter McGrath, Donald Grahame Holmes, "Multicarrier PWM strategies for multilevel inverters" IEEE Trans. On Ind.l Electronics, vol. 49, no. 4, 2002