# A Parallel Input Series Output DC/DC Converter with High Voltage Gain

## Ajmal M M<sup>1</sup>, Benny Cherian<sup>2</sup>, Babu Thomas<sup>3</sup>

<sup>1</sup>PG Scholar, Dept. of EEE, Mar Athanasius College of Engineering, Kothamangalam, Kerala, India, <sup>2</sup>Professor, Dept. of EEE, Mar Athanasius College of Engineering, Kothamangalam, Kerala, India, <sup>3</sup>Assistant Professor, Dept. of EEE, Mar Athanasius College of Engineering, Kothamangalam, Kerala, India

**Abstract** - The importance of high voltage gain dc/dc converter is increasing day by day. Conventional boost converter is unable to provide high gain without extreme duty ratio. An input parallel output series boost converter can provide a high step up gain. The converter uses two switches, two coupled inductors and a voltage multiplier module. The primary windings of coupled inductors are placed across the supply. Their connection reduces the input current ripple as it is shared by windings. The converter has high voltage gain and low voltage stress across power switches. The switches are turned on at zero current due to the leakage inductance of coupled inductor .The simulation of the converter is done in MATLAB/SIMULINK and results are obtained.

*Key Words*: High step up gain, DC/DC converter, Low voltage stress, Coupled inductors.

#### 1. INTRODUCTION

High gain dc/dc converters are widely used in many industrial applications such as solar, fuel cell, x-rays, laser and high intensity discharge lamp ballasts for automobile headlamps[2]-[4]. Theoretically, a basic boost converter is capable of providing high conversion ratio, but extremely high duty ratio is required. In practice, extreme duty ratios are not permitted because of the large conduction losses and frequent damage of power switches. Usually it is preferable to use low voltage rated power switches having low on state resistance to reduce the conduction losses, which may not be possible in a conventional boost converter. Cascaded boost converters can provide high voltage gain[5]-[6]. But high voltage stress across the switches and poor efficiency are the disadvantages. DC/DC converters using coupled inductors is a good alternative to obtain a high step up gain[7], provided the leakage inductances are handled properly. Interleaved control is found very useful in reducing the input current ripple of the converter[8]-[10]. Two different boost converter structures can be combined to produce twice the voltage gain by connecting there inputs in parallel and output in series. The two independent inductors of this combined converter is replaced by two coupled inductors. Connecting the primary windings of coupled inductors in parallel and secondary windings in series a high step up DC/DC converter is derived. An input parallel output series boost converter with dual coupled inductors can be used for high step up and high power applications. The interleaved control adopted reduces the input current ripple considerably. This configuration inherits the merits of high voltage gain, low voltage stress across the power switches and low output voltage ripple. Also, the converter is capable to turn on the active switches at zero current and hence reduce switching losses.

# 2. PARALLEL INPUT SERIES OUTPUT DC/DC CONVERTER

# 2.1 Input parallel output series boost converter

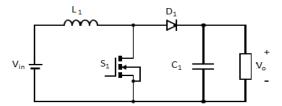

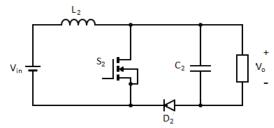

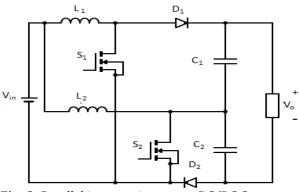

The input parallel output series concept is explained in Fig -1 to 3. The basic boost converter topology is shown in Fig -1 and Fig -2 is another boost version with the same function in which the output diode is placed on the negative dc rail. Fig -3 is called a modified interleaved boost converter, which is an input-parallel and output-series configuration derived from two basic boost types. The derived converter has twice the voltage gain of a conventional boost converter, low output voltage ripple and low input current ripple due to interleaved control.

**Fig -1**:Boost converter type1

Fig -2: Boost converter type2

ngineering and Technology (IRJET) e-ISSN: 2395 -0056 www.irjet.net p-ISSN: 2395-0072

Volume: 04 Issue: 04 | Apr -2017

Fig -3: Parallel input series output DC/DC Converter

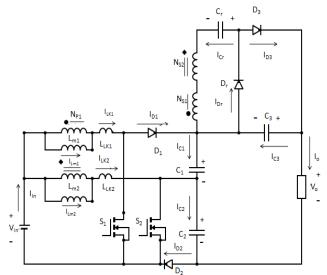

The separate inductors of Fig - 3 are modified by coupled inductors whose primary windings are connected in parallel and secondary windings in series as shown in Fig - 4. A voltage multiplier module is connected in the output to get a higher voltage gain. This connection has several advantages compared to conventional interleaved boost converter.

**Fig -4**: Input parallel output series DC/DC converter with high voltage gain

## 2.2 Operation of the converter

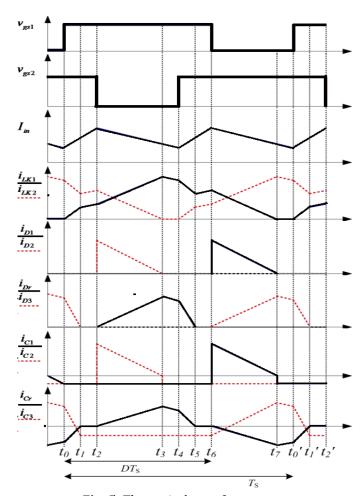

The converter is operated in continuous conduction mode(CCM).  $180^{\circ}$  interleaved overlapped pulses (Duty ratio greater than 50%) are used for the power switches. There are three switching states as S1 : ON, S2 : ON; S1 : ON, S2 : OFF; S1: OFF, S2 : ON. Operation of the converter can be explained through eight modes in the above mentioned control scheme. The basic working principle is as explained below. The theoretical waveforms of the converter are shown in Fig -5. The schematic diagram in each operating mode is shown in Fig -6 to Fig -13.

Fig -5: Theoretical waveforms

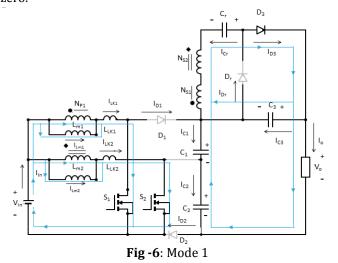

**Mode 1[t<sub>0</sub>-t<sub>1</sub>]:-** At t=t<sub>0</sub> Switch  $S_1$  is turned on at zero current switching due to the leakage inductance of  $L_{K1}$ .  $S_2$  remains turned on from the previous state as shown in Fig -6. All diodes except output diode  $D_3$  is turned off. This phase ends when the current through  $D_3$  decreases to zero.

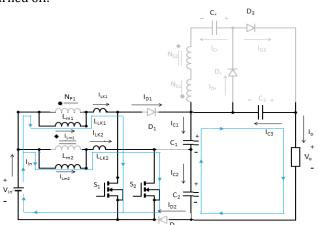

**Mode 2[t\_1-t\_2]:-** In this stage the power switches  $S_1$  and  $S_2$  remains turned on, as shown in Fig -7. All of the diodes are

ngineering and Technology (IRJET) e-ISSN: 2395 -0056

Volume: 04 Issue: 04 | Apr -2017 www.irjet.net p-ISSN: 2395-0072

reversed-biased. The voltage source  $V_{\rm in}$  charges magnetizing inductances  $L_{\rm m1}$  and  $L_{\rm m2}$  as well as leakage inductances  $L_{\rm k1}$  and  $L_{\rm k2}$ . This stage ends at  $t_2$ , when  $S_2$  is turned off.

Fig -7: Mode 2

$\label{eq:mode_sum} \begin{tabular}{ll} \textbf{Mode 3[t_2-t_3]:-} & The switch $S_2$ is turned off at $t=t_2$, hence the diodes $D_2$ and $D_r$ turned on. The current flow direction is shown in Fig -8. The energy that has stored in magnetizing inductance $L_{m2}$ is transferred to the secondary side, charging the capacitor $C_r$ through $D_r$. The input voltage source $V_{in}$, magnetizing inductance $L_{m2}$ and leakage inductance $L_{k2}$ deliver energy to the capacitor $C_2$ through diode $D_2$.}$

Fig -8: Mode3

**Mode 4[t<sub>3</sub>-t<sub>4</sub>]:-** when the total energy of leakage inductance  $L_{k2}$  has been completely delivered to the capacitor  $C_2$  at  $t=t_3$ , diode  $D_2$  automatically switches off. The current flow path of this stage is shown in Fig -8. Magnetizing inductance  $L_{m2}$  will transfer energy to the secondary side charging the capacitor  $C_r$  through diode  $D_r$ . The sum of currents of the magnetizing inductances  $L_{m1}$  and  $L_{m2}$  flows through the switch  $S_1$ .

Fig -9: Mode 4

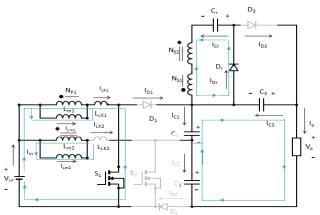

**Mode 5[t<sub>4</sub>-t<sub>5</sub>]:-** The switch  $S_1$  remains turned on at  $t=t_4$ , the switch  $S_2$  is turned on with ZCS due to the leakage inductance  $L_{k2}$ . The current flow direction of this stage is shown in Fig -10. This stage ends when the current through the diode  $D_r$  reduces to zero at  $t=t_5$ .

**Fig -10**: Mode 5

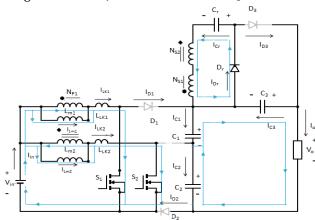

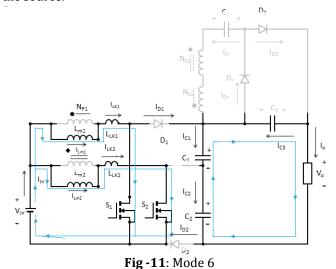

**Mode 6[t<sub>5</sub>-t<sub>6</sub>]:-** Operating modes 2 and 6 are same. All diodes are turned off. The magnetizing inductances  $L_{m1}$ ,  $L_{m2}$ , and the leakage inductances  $L_{k1}$ ,  $L_{k2}$  are charged by the source.

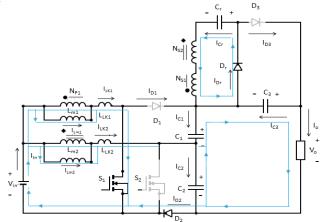

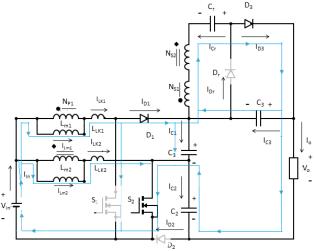

**Mode 7[t<sub>6</sub>-t<sub>7</sub>]:-** The switch  $S_2$  remains turned on. Switch  $S_1$  gets turned off at  $t = t_6$ . Which bring  $D_1$  and  $D_3$  into

www.irjet.net p-ISSN: 2395-0072

Volume: 04 Issue: 04 | Apr -2017

conduction. The current flow path of this stage is shown in Fig -12. The source  $V_{in}$ ,  $L_{m1}$  and  $L_{k1}$  together release their energy to the capacitor C<sub>1</sub> through the switch S<sub>2</sub>. At the same time, the energy stored in  $L_{m1}$  is released to the secondary side. D<sub>3</sub> is conducting and the current through the secondary sides will flow to load and capacitor C<sub>3</sub>.

Fig -12: Mode 7

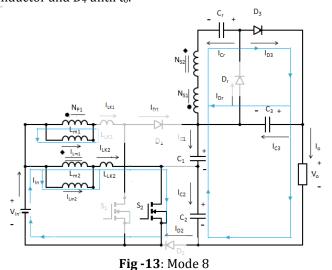

Mode  $8[t_7-t_8]$ :- At time  $t = t_7$ , diode  $D_1$  gets turned off because the total energy of leakage inductance  $L_{k1}$  has been completely transferred to the capacitor C<sub>1</sub>. The current of the magnetizing inductance L<sub>m1</sub> continues to flow to the output through the secondary side of coupled inductor and D<sub>4</sub> until t<sub>0</sub>.

3. CIRCUIT ANALYSIS AND DESIGN

#### 3.1 Voltage gain expression

Take two identical coupled inductors. Using the voltsecond balance principle on magnetizing inductances  $L_{m1}$ and  $L_{m2}$  respectively, the voltage gain  $(m_{CCM})$  can be obtained as, [1]

$$m_{CCM} = \frac{2(kN+1)}{1-D} \tag{1}$$

e-ISSN: 2395 -0056

Where k is the leakage factor of coupled inductors, N is the turns ratio and D is the duty ratio.

#### 3.2 Voltage stress analysis

To simplify the voltage stress analyses of the components, the leakage inductance of coupled inductor and the voltage ripples on the capacitors are ignored. The voltage stresses on power switches S<sub>1</sub> and S<sub>2</sub> for an output voltage V<sub>0</sub> are derived as, [1]

$$V_{S1} = V_{S2} = \frac{V_0}{2(1+N)} \tag{2}$$

#### 3.3 Coupled inductor design

From the voltage gain equation, the turns ratio of coupled inductor can be designed as, [1]  $N = \frac{m_{CCM}(1-D)}{2k} - \frac{1}{k}$

$$N = \frac{m_{CCM}(1-D)}{2k} - \frac{1}{k} \tag{3}$$

#### 3.4 Capacitor design

The filter capacitors are designed considering the voltage ripple( $\Delta V_C$ ) across it, for switching frequency  $f_s$  and load resistance R the capacitor values are estimated according to below equations [1]

$$C_1 \ge \frac{DV_0}{\Delta V_{C1}Rf_c} \tag{4}$$

$$C_2 \ge \frac{DV_0}{\Delta V_{C2}Rf_c} \tag{5}$$

$$C_3 \ge \frac{DV_0}{\Delta V_{C3}Rf_s} \tag{6}$$

$$C_r \ge \frac{V_0}{\Delta V_{Cor} R f_0} \tag{7}$$

#### 2. SIMULATION AND RESULTS

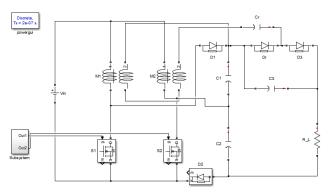

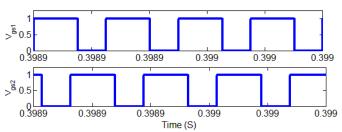

The converter is simulated in MATLAB/simulink and simulation results are obtained. The simulink model of the converter is shown in Fig -14. The pulse generation circuit is shown as a subsystem. 1800 interleaved overlapped pulses are used. The control signals with duty ratio 0.5 are shown in Fig -15. The simulation parameters are shown in table 1.

# International Research Journal of Engineering and Technology (IRJET)

Fig -14: Simulink model IPOS high gain converter

Fig -15: Control pulses of switches

**Table -1:** Simulation parameters.

| Parameter                                   | Value   |

|---------------------------------------------|---------|

| Po                                          | 100W    |

| V <sub>in</sub>                             | 20      |

| Magnetizing inductance, $L_{m1}$ , $L_{m2}$ | 242 μ Η |

| Capacitors C <sub>1</sub> , C <sub>2</sub>  | 47 μ F  |

| Capacitor C <sub>3</sub>                    | 100 μ F |

| Capacitor C <sub>r</sub>                    | 10 μ F  |

| Switching frequency, f <sub>s</sub>         | 40kHz   |

| $V_{\mathrm{out}}$                          | 200     |

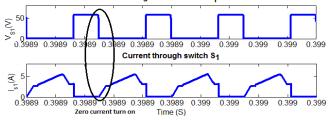

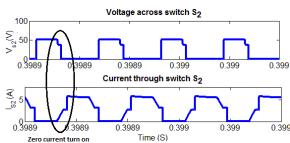

Fig - 16, 17 respectively shows the voltage across and current flowing through the switches 1 and 2. The voltage stress across the switch is a quarter of the output and switches are turned on at zero current.

**Fig -16**: Soft switching of switch S<sub>1</sub>

e-ISSN: 2395 -0056

Fig -17: Soft switching of switch S<sub>2</sub>

It is clear from the waveforms that the switches are turned on with zero current turn on due to the leakage inductance present in the path and hence switching losses are reduced.

Fig -18: Output voltage waveform Voltage acrosss diode D<sub>1</sub>

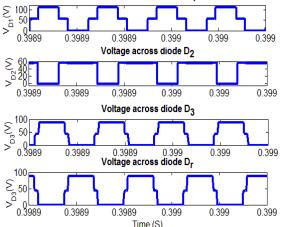

Fig -19: Voltage stress across diodes Current through diode D<sub>1</sub>

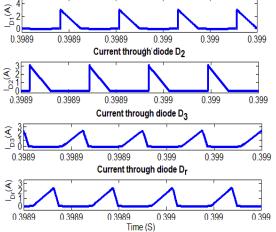

Fig -20: Current through diodes

# International Research Journal of Engineering and Technology (IRJET)

Fig -21: Ripple comparison

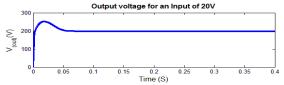

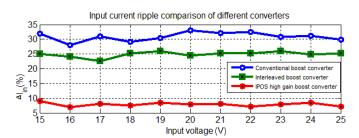

The output voltage with an input of 20V shown in Fig - 18 proves that the converter achieves the expected voltage gain with a low duty ratio of 0.6. Fig -19 and Fig -20 respectively show the voltage across and current flowing through the diodes. Ripple comparison shown in Fig -21 proves that the converter has a very less input current ripple compared to conventional boost/interleaved boost converter.

#### 3. CONCLUSIONS

An parallel input series output DC/DC converter using dual coupled inductors is found to be a good candidate for low input voltage, high voltage gain applications. The converter can achieve a much higher voltage gain and avoid operating at extreme duty cycle and numerous turn's ratios. A voltage gain of 10 is obtained by operating at a duty ratio of 0.6 with turns ratio 1. The voltage stresses of the power switches are very low, which is 25% of the output voltage. Interleaved control reduces the input current ripple effectively. The output voltage ripple is calculated as 0.02%. The simulation results show that main switches can be turned on at zero current.

#### REFERENCES

- [1] Xuefeng Hu, Chunying Gong, "A high gain inputparallel output-series dc/dc converter with dual coupled inductors" IEEE Transactions on Power Electron., vol. 30, no. 3, pp. 1306–1317, March. 2015.

- [2] Florent Boico, Brad Lehman, and Khalil Shujaee, "Solar battery chargers for NiMH batteries," IEEE Transactions on Power Electron., vol. 22, no. 5, pp. 1600–1609, Sep. 2007.

- [3] Z. Amjadi and S. S. Williamson, "Power-electronics-based solutions for plug-in hybrid electric vehicle energy storage and management systems," IEEE Trans. Ind. Electron., vol. 57, no. 2, pp. 608–616, Feb. 2010.

- [4] G. Fontes, C. Turpin, S. Astier, and T. A. Meynard, "Interactions between fuel cell and power converters: Influence of current harmonics on a fuel cell stack," IEEE Trans. Power Electron., vol. 22, no. 2, pp. 670–678, Mar. 2007.

- [5] S. Chen, T. Liang, L. Yang, and J. Chen, "A cascaded high step-up dc-dc converter with single switch for microsource applications," IEEE Trans. Power Electron., vol. 26, no. 4, pp. 1146–1153, Apr. 2011

- [6] S.V, J-P F, and Y. L, "Optimization and design of a cascaded DC/DC converter devoted to grid connected

Photovoltaic systems," IEEE Trans.Power Electron., vol. 27, no. 4, pp. 2018–2027, Apr. 2012.

e-ISSN: 2395-0056

- [7] S.V, J-P F, and Y. L, "Optimization and design of a cascaded DC/DC converter devoted to grid connected Photovoltaic systems," IEEE Trans.Power Electron., vol. 27, no. 4, pp. 2018–2027, Apr. 2012.

- [8] W. Li, Y. Zhao, J.Wu and X. He, `Interleaved high stepup converter with winding-cross-coupled inductors and voltage multiplier cells", *IEEE Transactions on Power Electronics*, vol. 27, no. 1, pp. 133143, Jan. 2012

- [9] G A. L. Henn, R. N. A. L. Silva, P P. Praca, L H. S. C. Barreto, and D S.Oa, Jr. Interleaved-boost converter with high voltage gain", *IEEE Transactions on Power Electronics*, vol. 25, no. 11,pp. 27532761, Nov. 2010.

- [10] C. M. Lai, C. T. Pan, and M. C. Cheng High effciency modular high step up interleaved boost converter for DC microgrid applications" *IEEE Transactions Industrial Applications*, vol. 48, no. 1, pp. 161171, Jan/Feb, 2012.

- [11] Zhe Zhang Coupled inductor magnetics in power electronics" Thesis for the partial fulfillment of the requirement of degree of doctor of philosophy, California Institute of Technology, 1987.