e-ISSN: 2395-0056 p-ISSN: 2395-0072

## Closed Loop Control of Hybrid Boosting Converter for Renewable **Energy Application**

### BHAVANASI ANUSHA<sup>1</sup>, M. SHIVA KUMAR<sup>2</sup>, M. SHOBBHA<sup>3</sup>, V.SURYA PRAKASH<sup>4</sup>

Abstract: This paper shows another hybrid boosting converter is utilized to build the input dc voltage. In Existing method hybrid boosting converter utilized with one switch in the converter and create pulses for that switch in open circle. By utilizing the open circle method we get just output as delivered measure of input which is given. Furthermore, we propose a shut circle method for HBC in this project. By utilizing this shut circle control technique we achieve required output voltage.

### I. Introduction

As of late, the brisk change of sustainable power source system calls for new generation of high gain dc/dc converters with high productivity and minimal effort. The front end of "attachment and Play" PV system normally asks for wander up converter which is fit for boosting the voltage from 35 to 380V with control ability because of the low terminal voltage and the essential of MPPT following limit with respect to single PV board .Considering a breeze develop with inward mediumvoltage dc (MVDC)- system, a MVDC converter prepared to help the voltage from 1-6 to 15-60 kV is required to associate the output of generator-facing rectifier to the MVDC line . Some other vitality stockpiling systems, for instance, power module filled system moreover require high-gain dc/dc converter because of their low voltage level at limit side. Remembering the ultimate objective to accomplish high voltage change extent with high capability, various high gain upgrade methodology were researched in the past distributions. Among them, switched capacitor structure, tapped/coupled inductorbased method, transformer-based strategy voltage multiplier structure or blends of them pulled in huge considerations. Each technology has its one of a kind favorable circumstances and confinements. The switched capacitor dc- dc converter can achieve high adequacy however has throbbing present and poor control limit. Introduction of thunderous switched capacitor converter can relieve the throbbing current however does not comprehend the control issue.

The tapped-inductor and transformer encourages gain boosting capacity however requires snubber circuit to handle leakage issue. The bend of above headways as a general rule outputs promising circuit incorporates however with over the top number of parts. In this paper, gain change development in light of alteration of standard help converter while keeping up single inductor and single switch is analyzed, centering at enhancing the circuit configuration, diminishing the cost,

satisfying the solicitations of common high gain applications, what's all the more, reassuring expansive scale fabricating. Gain upgrade from a help converter started from quadratic support. It accomplished higher voltage gain with a lone switch, yet exhibited high section voltage stretch. Regardless, this converter influenced high gain converter headway take after on.

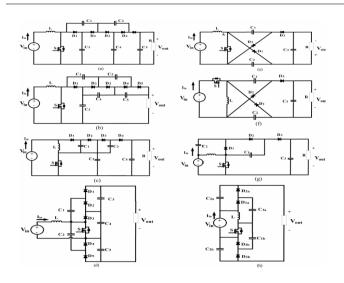

Many gain development procedures for help converter by including just diodes and capacitors were inspected already. The procedure for uniting support converter with standard Dickson multiplier what's more, Cockcroft- Walton multiplier to make new topologies were proposed, for instance, topologies in Fig. 1(a) what's more, (b). Air center inductor or stray inductor was used inside voltage multiplier unit to diminish current throb. A fundamental circuit using the super lift procedure was proposed and stretched out to higher gain applications such as Fig. 1(c). Its accomplice of negative output topology and twofold outputs topology were proposed and analyzed furthermore. The possibility of multilevel help converters was researched in and the topology of Fig. 1(d) was given as central source affiliation converter. Additionally, two switched capacitor cells were proposed and different topologies were dictated by applying them to the basic PWM dc- dc converters. Conventional topologies are showed up as Fig. 1(e) and (f). A changed voltage-lift cell was proposed and the topology of Fig. 1(g) was made. Propelled by the above topologies, another blend boosting converter (HBC) with single switch and single inductor is proposed by using bipolar voltage multiplier (BVM) in this paper.

The second-arrangement HBC is showed up as Fig. 1(h). Taken a gander at with other recorded topologies in Fig. 1, the proposed converter diminishes the voltage rating of output channel capacitor and showcases the nature interleaving operation properties. Differentiated and the converter in Fig. 1(d), the proposed converter has tinier

© 2017, IRJET **Impact Factor value: 6.171** ISO 9001:2008 Certified Journal | Page 1179

### **International Research Journal of Engineering and Technology (IRJET)**

Volume: 04 Issue: 12 | Dec-2017

www.irjet.net

e-ISSN: 2395-0056 p-ISSN: 2395-0072

Fig. 1. Previous high-gain dc-dc converters with singleswitch single-inductor and proposed topology. (a) Boost + Dickson multiplier, (b) Boost + Cockcroft-Walton multiplier, (c) super lift with elementary circuit, (d) central source multilevel boost converter, (e) Cuk derived, (f) Zeta derived, (g) modified voltage lifter, and (h) proposed second-order HBC.

Output ripple and higher parts use rate as for change ratio. Some interleaving progresses for swell decline and power improvement were represented in the composition; however these systems are commonly in perspective of circuit branch advancement which requires more parts. The proposed topology has accomplished humbler swell with single switch what's more, single inductor while keeping up high voltage gain.

## 2. Simulation Models and Results Proposed method

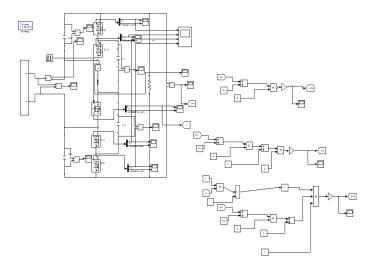

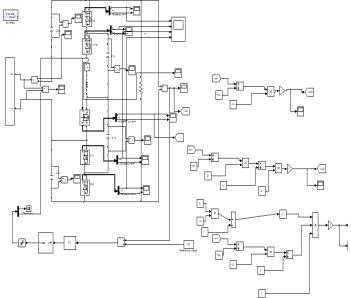

Fig.2 Simulation model of the HBC converter in proposed method

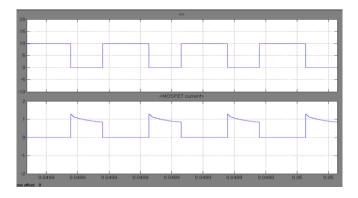

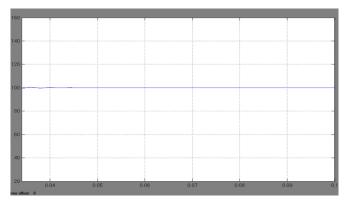

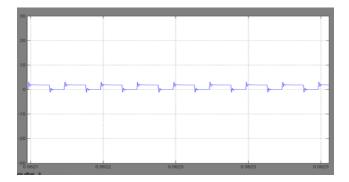

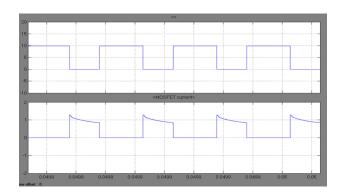

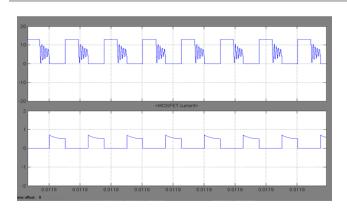

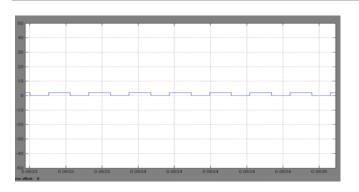

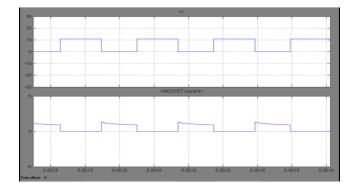

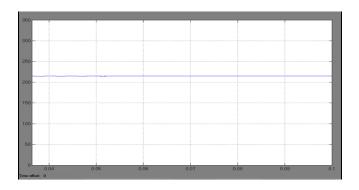

Fig. 3 a Simulation waveforms. Vds and Ids

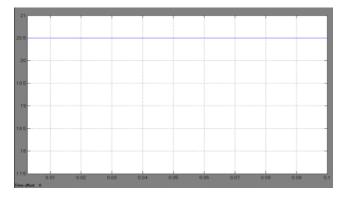

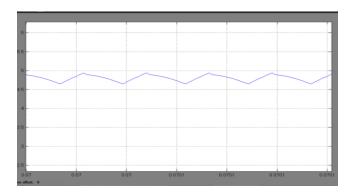

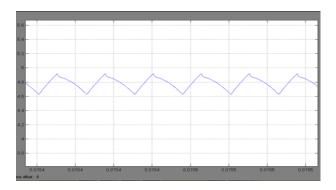

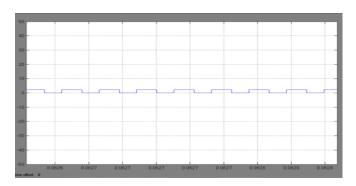

Fig. 3.b Simulation waveforms. Iin

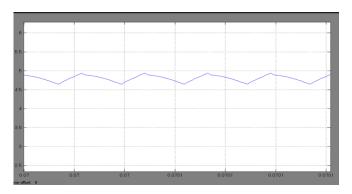

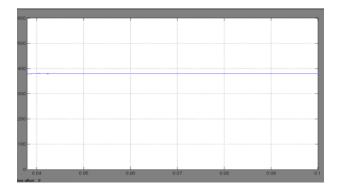

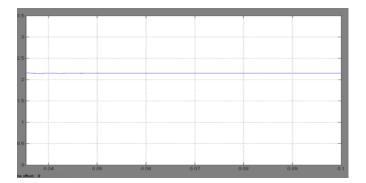

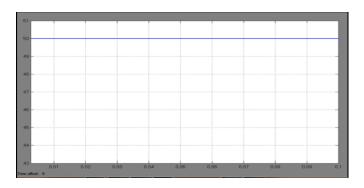

Fig. 3.c Simulation waveforms. Vout

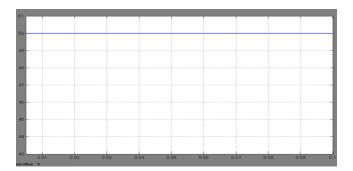

Fig. 3.d Simulation waveforms. Vin

www.irjet.net

e-ISSN: 2395-0056 p-ISSN: 2395-0072

Volume: 04 Issue: 12 | Dec-2017

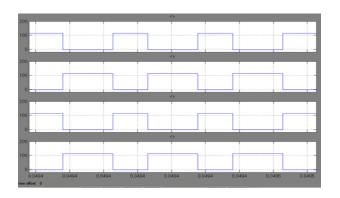

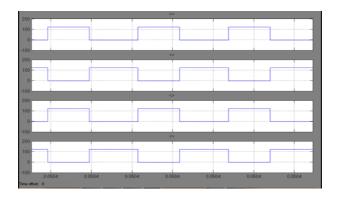

Fig. 3 e. Simulation waveforms. Diodes voltage:  $V_{d2a}$ ,  $V_{d1a}$ ,  $V_{d1b}$ ,  $V_{d2b}$

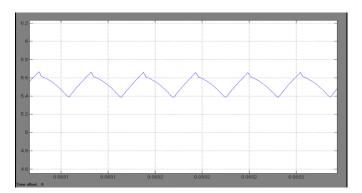

Fig. 4.a Simulation waveforms of voltage ripples under (a) D = 0.5,  $V_{c2a}$

Fig. 4 b . Simulation waveforms of voltage ripples under (a) D = 0.5,  $V_{c2b}$

Fig. 4. C. Simulation waveforms of voltage ripples under (a) D = 0.5,  $V_{out}$

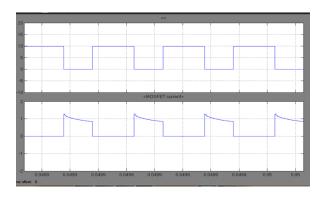

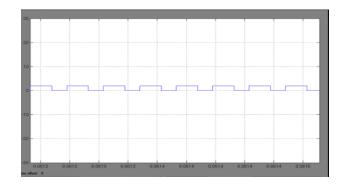

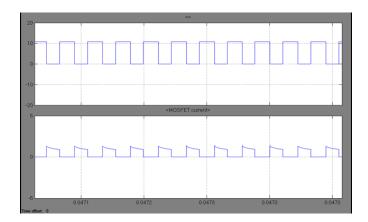

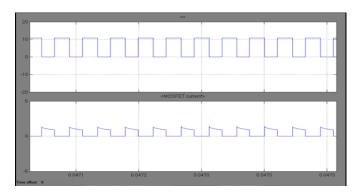

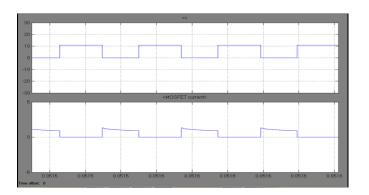

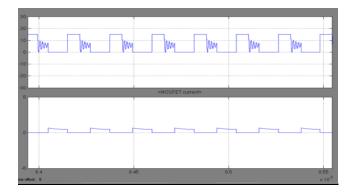

Fig. 4 d. Simulation waveforms of voltage ripples under (a) D = 0.5,  $V_{gs}$  and  $I_{gs}$

Fig. 4.e, Simulation waveforms of voltage ripples under (a) D = 0.8,  $V_{c2a}$

Fig. 4. F. Simulation waveforms of voltage ripples under (a) D = 0.8,  $V_{c2b}$

Fig. 4.g. Simulation waveforms of voltage ripples under (a) D = 0.8,  $V_{out}c$

e-ISSN: 2395-0056 p-ISSN: 2395-0072

Volume: 04 Issue: 12 | Dec-2017

Fig. 4.h. Simulation waveforms of voltage ripples under (a) D = 0.8,  $V_{gs}$  and  $I_{gs}$

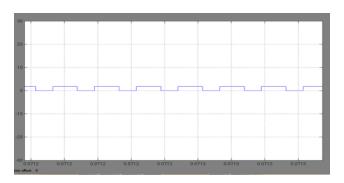

Fig. 5.a Simulation waveforms of under (a) BRM condition  $V_{out}$

Fig. 5.b Simulation waveforms of under (a) BRM condition  $V_{\rm in}$

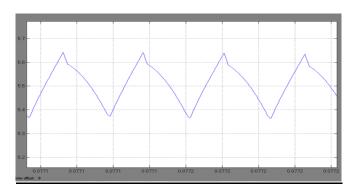

Fig. 5.c Simulation waveforms of under (a) BRM condition  $I_{\rm L}$

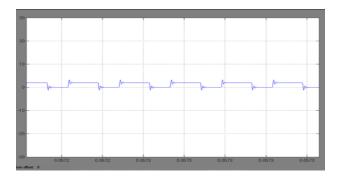

Fig. 5.d Simulation waveforms of under (a) BRM condition  $V_{ds}$  and  $I_{ds}$

Fig. 6.a Simulation waveforms of under (b) DCM condition  $V_{out}$

Fig. 6.b Simulation waveforms of under (b) DCM condition  $V_{\rm in}$

Fig. 6.c Simulation waveforms of under (b) DCM condition  $I_L$

Volume: 04 Issue: 12 | Dec-2017

www.irjet.net

Fig. 6.d Simulation waveforms of under (b) DCM condition  $V_{ds}$  and  $I_{ds}$

e-ISSN: 2395-0056

p-ISSN: 2395-0072

Fig. 8.b Simulation waveforms in Extension I<sub>in</sub>

# 3. Simulation Models and Results in Extension

Fig 7 Simulation model of the HBC converter in Extension method

Fig. 8. C Simulation waveforms in Extension Vout

Fig. 8.d Simulation waveforms in Extension  $V_{\rm in}$

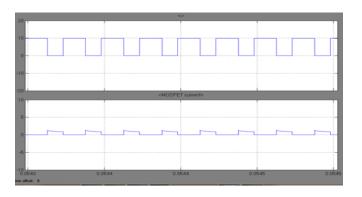

Fig. 8.a Simulation waveforms in Extension  $V_{ds}$  and  $$I_{ds}$$

Fig. 8.e Simulation waveforms in Extension Diodes voltage:  $V_{d2a}$  ,  $V_{d1a}$  ,  $V_{d1b},\,V_{d2b}$

e-ISSN: 2395-0056 p-ISSN: 2395-0072

Volume: 04 Issue: 12 | Dec-2017

Fig. 9.a Simulation waveforms of voltage ripples in Extension D=0.5:  $V_{c2a}$

Fig. 9.b Simulation waveforms of voltage ripples in Extension D=0.5:  $V_{c2b}$

Fig. 9.c Simulation waveforms of voltage ripples in Extension D=0.5: V<sub>out</sub>c

Fig. 9. D. Simulation waveforms of voltage ripples in Extension D=0.5:  $V_{ds}$  and  $I_{ds}$

Fig. 9.e Simulation waveforms of voltage ripples in Extension D=0.8:  $V_{c2a}$

Fig. 9.f Simulation waveforms of voltage ripples in Extension D=0.8:  $V_{c2b}$

Fig. 9. g. Simulation waveforms of voltage ripples in Extension D=0.8:  $V_{outc}$

Fig. 9. h. Simulation waveforms of voltage ripples in Extension D=0.8:  $V_{ds}$  and  $I_{ds}$

Fig. 10.a Simulation waveforms in BVM in Extension: Vout

Fig. 10. b. Simulation waveforms in BVM in Extension: Vin

Fig. 10.c Simulation waveforms in BVM in Extension:  $\mathbf{I}_{\mathbf{L}}$

Fig. 10.d Simulation waveforms in BVM in Extension: V<sub>ds</sub> and I<sub>ds</sub>

Fig. 11.a Simulation waveforms in DCM in Extension: Vout

Fig. 11.b. Simulation waveforms in DCM in Extension:  $V_{in}$

Fig. 11. c. Simulation waveforms in DCM in Extension: IL

Fig. 11.d Simulation waveforms in DCM in Extension: V<sub>ds</sub> and I<sub>ds</sub>

### International Research Journal of Engineering and Technology (IRJET)

Volume: 04 Issue: 12 | Dec-2017 www

### www.irjet.net

## CONCLUSION:

This paper exhibits another HBC utilized here for boosting the input low voltage to high level voltage. In this project we needs required sum or high voltage so we go for close circle or input method by utilizing criticism method we take output voltage as criticism and contrast that voltage and reference voltage or required voltage and provide for PI controller and we tuned the blunder and delivers pulses for switch which is utilized as a part of hybrid boost converter. These pulses for switch utilized as a part of the converter changes as indicated by what measure of output voltage creates yet in proposed method we get just a single output and change that output due to there is no criticism yet in expansion method we utilize input we get required measure of voltage until the point when the input give flags and pulses are change as per these signs we get output.

### **REFERENCES:**

- [1] W. Chen, A. Q. Huang, C. Li, G. Wang, and W. Gu, "Analysis and comparison of medium voltage high power DC/DC converters for offshore wind energy systems," IEEE Trans. Power Electron., vol. 28, no. 4, pp. 2014–2023, Apr. 2013.

- [2] J. A. Starzyk, "A DC-DC charge pump design based on voltage doublers," IEEE Trans. Circuits Syst. I Fundam. Theory Appl., vol. 48, no. 3, pp. 350–359, Mar. 2001.

- [3] F. L. Luo and H. Ye, "Positive output multiple-lift push-pull switched capacitor luo-converters," IEEE Trans. Ind. Electron., vol. 51, no. 3, pp. 594–602, Jun. 2004.

- [4] N. Vazquez, L. Estrada, C. Hernandez, and E. Rodriguez, "The tappedinductor boost converter," in Proc. IEEE Int. Symp. Ind. Electron., Jun. 2007, pp. 538–543.

- [5] R. Wai, C. Lin, R. Duan, and Y. Chang, "High-efficiency DC-DC converter with high voltage gain and reduced switch stress," IEEE Trans. Ind. Electron., vol. 54, no. 1, pp. 354–364, Feb. 2007.

- [6] J. Lee, T. Liang, and J. Chen, "Isolated coupled-inductor-integrated DC- DC converter with no dissipative snubber for solar energy applications," IEEE Trans. Ind. Electron., vol. 61, no. 7, pp. 3337–3348, Jul. 2014.

- [7] M. Delshad and H. Farzanehfard, "High step-up zero-voltage switching current-fed isolated pulse width modulation DC-DC converter," IET Power Electron., vol. 4, no. 3, pp. 316–322, Mar. 2011.

[8] A. Lamantia, P. G. Maranesi, and L. Radrizzani, "Small-signal model of the Cockcroft-Walton voltage multiplier," IEEE Trans. Power Electron., vol. 9, no. 1, pp. 18–25, Jan. 1994

e-ISSN: 2395-0056

p-ISSN: 2395-0072

- [9] P. Lin and L. Chua, "Topological generation and analysis of voltage multiplier circuits," IEEE Trans. Circuits Syst., vol. 24, no. 10, pp. 517–530, Oct. 1977.

- [10] K.-C. Tseng, C.-C. Huang, and W.-Y. Shih, "A high step-up converter with a voltage multiplier module for a photovoltaic system," IEEE Trans. Power Electron., vol. 28, no. 6, pp. 3047–3057, Jun. 2013.

- [11] W. Li, W. Li, X. Xiang, Y. Hu, and X. He, "High step-up interleaved converter with built-in transformer voltage multiplier cells for sustainable energy applications," IEEE Trans. Power Electron., vol. 29, no. 6, pp. 2829–2836, Jun. 2014.

- [12] X. Hu and C. Gong, "A high voltage gain DC–DC converter integrating coupled-inductor and diodecapacitor techniques," IEEE Trans. Power Electron., vol. 29, no. 2, pp. 789–800, Feb. 2014.

- [13] D. Cao and F. Z. Peng, "A family of zero current switching switched capacitor dc-dc converters," in Proc. 25th Annu. IEEE Appl. Power Electron. Conf. Expo., Feb. 2010, pp. 1365–1372.

- [14] J. Yao, A. Abramovitz, and K. Smedley, "Steep gain bidirectional converter with a regenerative snubber," IEEE Trans. Power Electron., vol. 8993, no. c, p. 1, 2015.

- [15] D. Maksimovic and S. Cuk, "Switching converters with wide DC conversion range," IEEE Trans. Power Electron., vol. 6, no. 1, pp. 151–157, Jan. 1991.

- [16] B. Axelrod, G. Golan, Y. Berkovich, and A. Shenkman, "Diode–capacitor voltage multipliers combined with boost-converters: Topologies and characteristics," IET Power Electron., vol. 5, no. 6, pp. 873–884, Jul. 2012.

- [17] M. Prudente, L. L. Pfitscher, G. Emmendoerfer, E. F. Romaneli, and R. Gules, "Voltage multiplier cells applied to converters, non-isolated DC–DC," IEEE Trans. Power Electron., vol. 23, no. 2, pp. 871–887, Mar. 2008.

- [18] F. L. Luo, S. Member, and H. Ye, "Positive output super-lift converters," IEEE Trans. Power Electron., vol. 18, no. 1, pp. 105–113, Jan. 2003.

- [19] F. L. Luo and H. Ye, "Negative output super-lift converters," IEEE Trans. Power Electron., vol. 18, no. 5, pp. 1113–1121, Sep. 2003. [20] F. L. Luo