# AREA EFFICIENT LOW ERROR COMPENSATION MULTIPLIER DESIGN USING FIXED WIDTH RPR

www.iriet.net

## N.MEGALA<sup>1</sup>, N.RAJESWARAN<sup>2</sup>

<sup>1</sup>PG scholar,Department of ECE, SNS College OF Technology , Tamil nadu, India. <sup>2</sup>Associate professor, Department of ECE, SNS College OF Technology , Tamil nadu, India.

#### ABSTRACT

In area efficient low error compensation multiplier design is using fixed width RPR(Reduced Precision Redundancy). We propose a new method called fixed width RPR for DSP applications. This fixed width multiplier is placed in ANT architecture to meet high speed, low power consumption and area efficiency. The fixed RPR is designed with compensation circuit for minimizing the occurrence of error. The nxn bit is used as a input. The partial product term is used in RPR block for input correction vector and trivial input modification vector to worse the truncation errors. To achieve more precise error compensation. Variable correction value is used the truncation error can be compensation circuit is minimized.

Volume: 02 Issue: 07 | Oct-2015

#### **KEY WORDS**

Algorithmic noise tolerant (ANT), fixed-width multiplier,reduced-precision replica (RPR),voltage overcalling(VOS) and error correction block(EC)

## **1. INTRODUCTION**

To lower the power indulgence, supply voltage scaling is broadly used as an effective low power technique. The power utilization in CMOS circuits is comparative to the square of supply voltage. The ANT architecture contains both main digital processor and error correction block. In ANT design we propose a fixed width RPR instead of full width RPR. RPR stands for reduced precision replica, if the original system computes the error,

the RPR output is taken as the corrected output. To achieve more precise compensation, we construct the

error compensation circuit mainly using the partial product term with largest weight in the LSB segment. By using compensation circuit we truncate the error with the help of variable correction vector. The disadvantage of the previous method is hardware complexity is high, voltage over scaling is used to reduce the error. This can be overcome by RPR method.

#### 2. ANT DESIGN

ANT can be mainly divided into Prediction based ANT and Reduced Precision Redundancy based ANT. Using ANT technique to recover the concert of DSP algorithms in presence of bit error rates. Therefore ANT can produce more efficient signals. ANT to balance for deprivation in the structure production due to errors from soft computations.

#### **3. FULL WIDTH MULTIPLIER DESIGN**

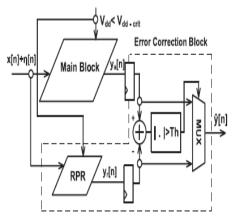

Fig. 1 ANT architecture using

This technique consists of main block and error correction block. To meet ultralow power demand. In

the ANT method a duplication of the MDSP(Main Digital Signal Processor) but with condensed precision operands and shorter computation delay is used as EC block. The input is given to the main block it process to produce the output as va[n]. RPR block simultaneously processed and produce the output as yr[n]. RPR output yr [n] is still correct since the critical path delay of the replica is smaller than Tsamp. Therefore, yr [n] is applied to detect errors in the MDSP output ya[n]. The error in the output is corrected by using voltage Error detection is accomplished by overscaling comparing the difference |ya[n] - yr [n]| against a threshold Th. Once the difference between ya[n] and vr [n] is larger than Th, the output  $\hat{v}[n]$  is vr [n] instead of ya[n]. As a result, y[n] can be expressed as

y[n] = ya [n],if  $|ya [n] - yr [n]| \le Th yr [n],$ if |ya [n] - yr [n]| > Th.....(1)Th is determined by Th = max |yo [n] - yr [n] |.....(2) Where yo[n] is error free output signal

## 4. PROPOSED FIXED WIDTH MULTIPLIER

The fixed-width multipliers have been widely used in digital signal processor(DSP) design due to their lower power dissipation and less area. In order to reduce the chip area many fixed width Booth multipliers have been used. They decrease the detection accurateness because of reduced partial products. This method can reduce the truncated error by using variable compensation value. In order to overcome the disadvantages we presented a method of dividing the reduced partial products into the foremost truncated section and the trivial shortened section.

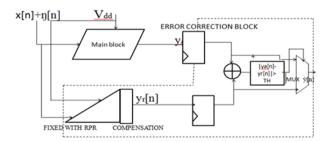

Fig. 2 proposed ANT architecture

The main block is implemented with the help of power supply VDD. The output of the main block is

produced and it is denoted by ya[n]. Simultaneously the RPR block also implemented the compensation circuit correct the truncated error and produce the output. The output of this block is denoted by yr[n]. Both the outputs are taken into the decision block. The threshold value is predefined we compare the both outputs ya[n] and yr[n]. The value is less than the threshold value the multiplexer produce the output as main block ya[n].It is consider as error free output. If the value is greater than the threshold value the multiplexer produce the output as yr[n].It is consider as error truncated value. The soft error in the output is minimized.

## 4.1. MAIN BLOCK

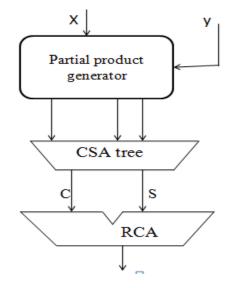

Fig. 3 Main Block diagram for proposed ANT design

In main block we are given nxn inputs to the partial product generator. The generator circuit generate the partial product terms. The output of the circuit is given to the CSA (Carry Save Adder)tree.CSA circuit group the product terms to produce two row outputs carry and sum bits. This process is iterated until all the partial product terms are grouped. Finally the output of CSA tree is given to the RCA(Ripple Carry Adder)circuit. The RCA circuit is processed based on the inputs size they finally produce the output of the main block. is operated with the help of power supply and its output is denoted by ya[n].

## 4.2. ERROR CORRECTION BLOCK

The error correction hunk which consist of multiplexer, RPR block compensation circuits and

registers. In error correction block the inputs are given to the RPR block. The function of the RPR block is to correct the errors occurring in the output. The RPR hunk take the input as partial products. If the input is 12x12 bits it takes half of the partial terms or MSB segments. The RPR only takes 6 bits for processing. Error in the output is minimized or truncated. After that the compensation circuit to compensate the truncated errors and finally produce the input we use RPR method. Mutually the outputs are taken to the decision block. This hunk is used for selecting the error free production. Mutual values are compared with threshold value the ultimate value is displayed. If the value is greater than the threshold value the RPR value is displayed or else main block output is displayed. This output is considered as a error free output. With the help of selection line the multiplier choose the correct output. The variable precision value is used to achieve good precision value. The input correction vector is used in error compensation circuit for compensating the errors. The error in the output is minimized.

## **5. SIMULATION RESULTS AND DISCUSSION**

In this zone, we converse about the concert of the proposed RPR ANT structure.

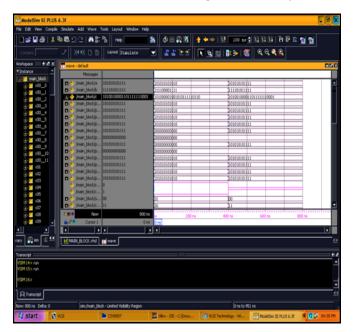

First, we define the main block, it is simulated by using MODELSIM software .Here two inputs are x and y.

Second, we define the EC block, error correction block is simulated by using MODELSIM software

Finally we define whole circuit output waveforms that is simulated by using MODELSIM software

# **6. CONCLUSION**

In order to evaluate the performance of design ,we have to compare the performance of this fixed width RPR design with previous full width RPR design. The design is synthesized by using Xilinx 8.1V.based on this modification soft digital signal processing systems that consume much less power than systems operating error-free at critical supply voltages Soft digital signal processing systems can reduce leakage power and provide robustness to errors caused by leakage currents.

## REFERENCES

[1] B. Shim, S. Sridhara, and N. R. Shanbhag, "Reliable low-power digital signal processing via reduced precision redundancy," IEEE Trans.Very Large Scale Integr. (VLSI) Syst., vol. 12, no. 5, pp. 497–510,May 2004.

[2] B. Shim and N. R. Shanbhag, "Energy-efficient softerror tolerant digital signal processing," IEEE Trans. Very Large Scale Integr. (VLSI) Syst.,vol. 14, no. 4, pp. 336–348, Apr. 2006. [3] R. Hedge and N. R. Shanbhag, "Energy-efficient signal processing via algorithmic noise-tolerance," in Proc. IEEE Int. Symp. Low Power Electron. Des., Aug. 1999, pp. 30–35.

[4] V. Gupta, D. Mohapatra, A. Raghunathan, and K. Roy, "Low-power digital signal processing using approximate adders," IEEE Trans. Comput. Added Des. Integr. Circuits Syst., vol. 32, no. 1, pp. 124–137, Jan. 2013.

[5] Y. Liu, T. Zhang, and K. K. Parhi, "Computation error analysis in digital signal processing systems with overscaled supply voltage," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 18, no. 4, pp. 517–526 Apr. 2010.

[6] J. N. Chen, J. H. Hu, and S. Y. Li, "Low power digital signal processing scheme via stochastic logic protection," in Proc. IEEE Int. Symp. Circuits Syst., May 2012, pp. 3077–3080.

[7] J. N. Chen and J. H. Hu, "Energy-efficient digital signal processing via voltage-overscaling-based residue number system," IEEE Trans.Very Large Scale Integr. (VLSI) Syst., vol. 21, no. 7, pp. 1322–1332,Jul. 2013.

[8] P. N. Whatmough, S. Das, D. M. Bull, and I. Darwazeh, "Circuit-level timing error tolerance for low-power DSP filters and transforms," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 21, no. 6, pp. 12–18, Feb. 2012.

[9] G. Karakonstantis, D. Mohapatra, and K. Roy, "Logic and memory design based on unequal error protection for voltage-scalable, robust and adaptive DSP systems," J. Signal Process. Syst., vol. 68, no. 3, pp. 415– 431, 2012.

[10] Y. Pu, J. P. de Gyvez, H. Corporaal, and Y. Ha, "An ultra low energy/frame multi-standard JPEG coprocessor in 65-nm CMOS with sub/near threshold power supply," IEEE J. Solid State Circuits, vol. 45, no. 3, pp. 668–680, Mar. 2010.

[11] H. Fuketa, K. Hirairi, T. Yasufuku, M. Takamiya, M. Nomura, H. Shinohara, et al., "12.7-times energy efficiency increase of 16-bit integer unit by power supply voltage (VDD) scaling from 1.2V to 310mV enabled by contention-less flip-flops (CLFF) and separated

VDD between flip-flops and combinational logics," in Proc. ISLPED, Fukuoka, Japan, Aug. 2011, pp. 163–168.

[12] Y. C. Lim, "Single-precision multiplier with reduced circuit complexity for signal processing applications," IEEE Trans. Comput., vol. 41, no. 10,pp. 1333–1336, Oct. 1992.

[13] M. J. Schulte and E. E. Swartzlander, "Truncated multiplication with correction constant," in Proc. Workshop VLSI Signal Process., vol. 6. 1993, pp. 388–396.

[14] S. S. Kidambi, F. El-Guibaly, and A. Antoniou, "Area-efficient multipliers for digital signal processing applications," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 43, no. 2, pp. 90–95, Feb. 1996.

[15] J. M. Jou, S. R. Kuang, and R. D. Chen, "Design of low-error fixed-width multipliers for DSP applications," IEEE Trans. Circuits Syst., vol. 46, no. 6, pp. 836–842, Jun. 1999.