# **Design of Low Power Architecture for Implantable Bio Medical Device**

Mrs. Lakshmi S V<sup>1</sup>, Shree Nitish B N<sup>2</sup>, Tamilarasan S<sup>3</sup>, Sathish G<sup>4</sup>, Prithiv Raj K<sup>5</sup>

<sup>1</sup> Assistant Professor, Dept. of Electronics and Communication Engineering, SNS College of Technology, Tamil Nadu, India

<sup>2</sup> Student, Dept. of Electronics and Communication Engineering, SNS College of Technology, Tamil Nadu, India

<sup>3</sup> Student, Dept. of Electronics and Communication Engineering, SNS College of Technology, Tamil Nadu, India

<sup>4</sup> Student, Dept. of Electronics and Communication Engineering, SNS College of Technology, Tamil Nadu, India

<sup>5</sup> Student, Dept. of Electronics and Communication Engineering, SNS College of Technology, Tamil Nadu, India \*\*\*\_\_\_\_\_\_

Abstract - Implantable Medical Devices (IMDs) are crucial for treating diverse medical conditions, prompting the development of integrated chips to address the need for smaller, lighter, and more power-efficient devices. These devices play a pivotal role in providing therapy for conditions such as heart disease, pain management, and neurological disorders. Advancements in nanotechnology have facilitated the creation of sub-micron-sized devices that positively impact physiological processes upon implantation. Examples like implantable cardiac pacemakers and deep brain stimulators allow patients with various disorders to lead normal lives. Key parameters for successful IMDs include small volume, long lifespan, low power consumption, high biocompatibility, and reliability. Despite their significance in modern healthcare, the challenge lies in balancing power consumption and performance, particularly with the increasing demand for complex treatment paradigms, as the longevity of battery life becomes crucial in the growing IMD market where frequent battery changes are impractical.

#### Key Words: Implantable Medical Devices (IMDs), Integrated Chip, Nanotechnology, Power Efficiency, Healthcare Advancements, Battery Life, Modern Medicine

# **1. INTRODUCTION**

In the present world, surgical implants, referred to as Implantable Medical Devices (IMDs), serve various medical purposes. The increasing clinical demand for implanted devices poses challenges such as the need to reduce size, weight, and power. Consequently, there is a necessity to develop an integrated chip specifically designed for implantable medical devices. These devices play a crucial role in providing therapy for a diverse range of conditions, including heart disease, pain management, Parkinson's disease, epilepsy, and psychiatric disorders. Advances in nanotechnology now enable interventions at sub-micron scales upon implantation, influencing physiological processes positively.

Examples like cardiac pacemakers, cochlear implants, and deep brain stimulators highlight how IMDs enhance patients' lives. Meeting parameters like small

volume, long lifespan, low power consumption, biocompatibility, and reliability is essential for these devices. Recent advancements in engineering and medicine have led to a downsizing trend in implanted medical devices, significantly impacting contemporary healthcare. The evolving Ultra Low Power (ULP) Electronics domain, driven by the intense integration of system-on-a-chip (SoC), addresses the increased power economy and performance demands for complex treatment paradigms in IMD applications. Achieving lower power consumption is crucial for extending battery life, especially as the IMD market expands, minimizing the need for frequent battery changes.

# 2. APPROACHES

Reducing the power consumption of implantable medical devices, such as pacemakers, involves a combination of innovative technologies and design strategies. Several approaches can be taken to achieve this goal:

# 2.1 Low-Power Electronics Design

Utilizing advanced low-power electronic components and circuitry is a fundamental approach. This includes employing low-power microcontrollers, energy-efficient sensors, and optimizing circuit designs to minimize power usage during device operation.

# 2.2 Energy – Efficient Algorithms

Implementing algorithms that are designed to be energyefficient is crucial. This includes optimizing signal processing algorithms, data compression techniques, and decisionmaking processes to reduce computational requirements and, consequently, power consumption.

# 2.3 Biocompatible Materials and Miniaturization

Choosing biocompatible materials for the device's construction and embracing miniaturization technologies not only reduces the overall size of the device but also contributes to energy efficiency by reducing the energy required for operation.

# **3. TECHNOLOGIES**

Several technologies are employed in pacemakers to ensure low power consumption, allowing for extended battery life and minimizing the need for frequent replacements. Some key technologies include:

## 3.1 Low-Power Microcontrollers:

Advanced microcontroller units designed for low power consumption play a crucial role in the efficient operation of pacemakers. These microcontrollers are optimized to perform necessary computations while consuming minimal energy, contributing to overall power efficiency.

## 3.2 Energy-Efficient Sensors:

Sensors integrated into pacemakers, such as accelerometers or physiological sensors, are chosen or designed to be energy-efficient. These sensors enable the device to respond to changes in the patient's physiological conditions while minimizing the impact on power consumption.

## 3.3 Advanced Battery Technologies:

The choice of battery technology significantly influences power consumption. Pacemakers often use lithium-based batteries with high energy density and low self-discharge rates. Research focuses on improving battery technologies to further reduce size, weight, and improve overall performance.

## **4. OBJECTIVE**

Reducing the power consumption of implantable medical devices, particularly in the case of devices like pacemakers, holds immense promise across various domains of healthcare. One of the most immediate and critical advantages is the extension of battery life. Implantable devices, reliant on batteries, often require surgical procedures for battery replacements. By minimizing power consumption, the frequency of these interventions can be significantly reduced, enhancing patient safety and minimizing the associated risks of invasive procedures.

Moreover, the scope of reducing power consumption contributes to an improved patient experience. Patients with implantable devices, such as pacemakers, benefit from prolonged device functionality, leading to a better quality of life. The reduced need for frequent medical interventions alleviates patient anxiety and provides a sense of security, knowing that the device is continuously and reliably operating.

Lower power consumption also opens doors to innovations in device functionality. With extended battery life, manufacturers can explore incorporating additional features and capabilities within the same device footprint. This might include advanced sensing technologies, more sophisticated algorithms for real-time monitoring, or wireless communication capabilities for remote healthcare management. These advancements can significantly enhance the scope and depth of medical insights and patient care.

Furthermore, the reduction in power requirements can lead to smaller and lighter devices. In the realm of implantable devices, particularly those that involve surgical implantation, minimizing size and weight is crucial for ease of implantation and patient comfort. This can also contribute to advancements in device design and materials, aligning with the ongoing trend towards miniaturization in medical technology.

Research and development in the field of Ultra Low Power (ULP) Electronics are central to achieving these goals. Advancements in energy-efficient circuitry, sensor technologies, and intelligent power management strategies are key components of efforts to reduce power consumption in implantable medical devices. In conclusion, the scope of minimizing power consumption in devices like pacemakers extends far beyond technical considerations; it profoundly impacts patient outcomes, healthcare efficiency, and the overall landscape of implantable medical technologies.

## **5. PROPOSED SYSTEM**

Pacemakers are engineered to optimize power consumption during periods of inactivity, strategically preserving the battery when the device is not actively pacing the heart. This efficiency is achieved through meticulous design, ensuring minimal power consumption during standby mode. Moreover, advancements involve modifying the Analog-to-Digital Converter (ADC) circuit to further reduce power usage, extending the overall battery life. These modifications focus on enhancing energy efficiency without compromising the device's ability to accurately sense and respond to the heart's electrical signals.

Additionally, there's a growing emphasis on incorporating advanced technologies such as machine learning or deep learning to enhance the efficiency of the algorithm used in the signal coprocessor. By leveraging these sophisticated computational techniques, pacemakers can optimize decision-making processes, improving the precision of signal interpretation and pacing interventions. This not only contributes to better patient outcomes but also potentially reduces power consumption by streamlining and optimizing algorithmic functions. As the field of medical electronics continues to evolve, the integration of cuttingedge technologies aims to enhance both the longevity and performance of pacemaker systems, ensuring sustained reliability in cardiac rhythm management.

# 6. HEART'S ELECTRICAL SYSTEM

The heart's electrical system is a complex network of specialized cells that generate and conduct electrical signals, orchestrating the rhythmic contractions of the heart muscle. This system ensures the synchronized pumping of blood

through the chambers of the heart and the coordination of the cardiac cycle.

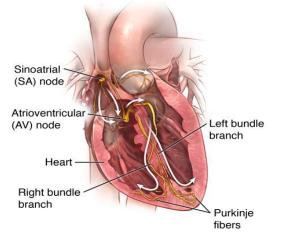

Fig-1: Electrical System of the Heart

#### 6.1 Sinoatrial (SA) Node

The electrical impulses that initiate each heartbeat originate in the sinoatrial (SA) node, often referred to as the heart's natural pacemaker. Located in the right atrium, the SA node generates electrical signals at regular intervals, establishing the heart's baseline rhythm. These signals stimulate the atria to contract, initiating the filling of the ventricles.

#### 6.2 Atrioventricular (AV) Node

The electrical impulses then travel to the Atrioventricular (AV) node, a cluster of cells between the atria and ventricles. The AV node acts as a relay station, briefly delaying the signals to allow the ventricles to fill completely before contracting.

#### 6.3 Bundle of His and Purkinje Fibers

From the AV node, the electrical signals travel through the Bundle of His, a bundle of specialized fibers that conduct the impulses into the ventricles. The Bundle of His further divides into Purkinje fibers, spreading the electrical signals throughout the ventricles, initiating their contraction.

#### **6.4 Atrial and Ventricular Contraction**

The electrical impulses cause the atria to contract first, pumping blood into the ventricles. Subsequently, the impulses reach the ventricles, leading to their contraction and the ejection of blood into the pulmonary artery and aorta, respectively.

## 6.5 Electrocardiogram (ECG or EKG)

The electrical activity of the heart can be visualized through an electrocardiogram (ECG or EKG). This diagnostic tool records the electrical signals as waves on a graph, providing valuable information about the heart's rhythm and any potential abnormalities.

## 7. CARDIAC PACE MAKER

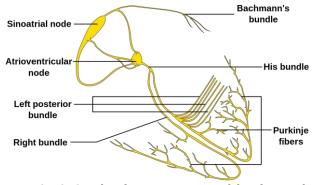

The contraction of cardiac muscle (heart muscle) is initiated by electrical impulses known as action potentials. The cardiac action potential is a brief change in voltage across the cell membrane of heart cells. This is caused by the movement of charged atoms between the inside and outside of the cell, through proteins called ion channels. The rate at which these impulses fire controls the rate of cardiac contraction, that is, the heart rate (Heart rate is the frequency of the heartbeat measured by the number of contractions of the heart per minute.)

The cell is the basic structural and functional unit of all forms of life. Every cell consists of cytoplasm enclosed within a membrane, and contains many macromolecules such as proteins, DNA and RNA, as well as many small molecules of nutrients and metabolites that create these rhythmic impulses, setting the pace for blood pumping, are called pacemaker cells, and they directly control the heart rate. They make up the cardiac pacemaker, that is, the natural pacemaker of the heart. In most humans, the highest concentration of pacemaker cells is in the sinoatrial (SA) node the natural and primary pacemaker, and the resultant rhythm is a sinus rhythm. The sinoatrial node is an oval shaped region of special cardiac muscle in the upper back wall of the right atrium made up of cells known as pacemaker cells.

**Fig -2:** Graphical representation of the electrical conduction system of the heart that maintains the heart rate in the cardiac cycle

## 8. PRESENT - ADVANCED SENSOR TECHNOLOGIES:

Ongoing research focuses on integrating advanced sensor technologies into pacemakers to enable more responsive and personalized pacing therapy.

Innovations in sensors aim to enhance the device's ability to adapt to the patient's physiological needs, providing more nuanced and individualized cardiac pacing. The evolution of pacemakers has been marked by continuous innovation, progressing from early concepts to sophisticated, miniaturized, and adaptive devices. Each milestone represents a significant stride in enhancing the effectiveness, safety, and quality of life for individuals with cardiac rhythm disorders.

A pacemaker is a small medical device designed to control and regulate the heartbeat by sending electrical pulses. It is often used to treat bradycardia, a condition caused by a slow heart rate. This device has two main parts: the generator and the cable. A generator is a small piece of metal with a battery and electricity. Batteries power the device and typically last several years before needing replacement. The electronic device contains а microprocessor that monitors the heart's electrical activity and determines when more electricity is needed to control the rhythm. Cables or electrodes are electrical cables that connect the pacemaker to the heart muscle. There are usually one to three administrators, depending on the patient's specific needs. These wires pass through the nerves and contact the tissues.

The cables carry electrical signals between the heart and the pacemaker, allowing the device to monitor the heart's activity and intervene when necessary.

Pacemakers work by sensing the heart's natural electrical activity and responding accordingly. When the heart rate drops below a preset value, indicating bradycardia, the pacemaker sends small electrical impulses to stimulate the heart muscle to contract. These electrical signals give rise to electrical impulses produced by the heart's own pacemaker, the sinoatrial (SA).

Modern pacemakers have features such as feedback that allow the device to adjust the heart rate according to the patient's activity level. For example, heart rate increases during pregnancy and decreases during rest. This change ensures that the patient's heart rate still matches their current needs. The pacemaker is also equipped with a telemetry feature that allows doctors to monitor it remotely. This allows doctors to evaluate the operation of the device, check for problems that need to be addressed, and make any necessary adjustments, without having to visit the person regularly. Pacemaker implantation is a simple procedure. The device is usually placed under the skin in the chest area and wires are passed through the arteries to the heart. The surgery is performed under local anesthesia and most patients experience discomfort during recovery. In summary, a pacemaker is a complex medical device designed to control and normalize heart rhythm. Pacemakers play an important role in treating bradycardia and improving the quality of life of people with this condition, monitoring the electrical activity of the heart and providing excellent electrical stimulation when needed.

#### 9. COMPONENTS OF PACEMAKER

- Pulse Generator

- Leads

- Electrodes

- Battery

- Comparator

- Amplifier

Table -1: Specification of the Battery

| Specification           | Characteristic                                                                  |

|-------------------------|---------------------------------------------------------------------------------|

| Chemistry               | Lithium-based (e.g.,<br>lithium-iodine, lithium-<br>silver vanadium)            |

| Voltage                 | 2.8 to 4.4 volts                                                                |

| Capacity (mAh)          | 400 to 900 mAh                                                                  |

| Self-Discharge Rate     | Low                                                                             |

| Longevity               | Several years to over a decade                                                  |

| Size and Form Factor    | Compact (coin-cell or cylindrical)                                              |

| Monitoring Capabilities | Advanced features for<br>assessing battery capacity<br>during routine check-ups |

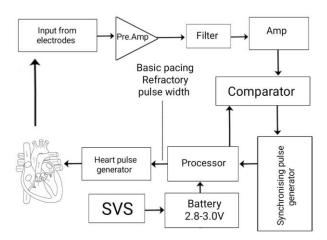

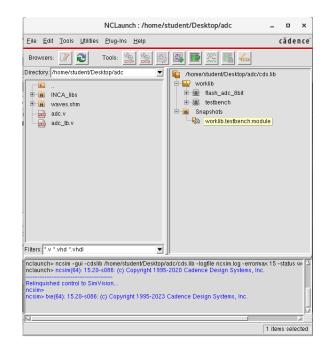

#### **10. WORKING OF PROPOSED SYSTEM**

This project is designed with electronic circuit design, biocompatible materials and Cadence software tool. This approach entails carefully planning the layout of the analog to digital converter of a pacemaker. The development of a reliable electronic system that can track the electrical signals coming from the heart and send electrical impulses as necessary. They take into account elements including power effectiveness, power consumption abilities and compatibility with the physical environment of the human body. To achieve precise detection and timely pacing, components such as sensors, amplifiers, and pacing circuits are meticulously developed and tuned. Using biocompatible materials and encapsulations that won't trigger an immune reaction or damage nearby tissues to make sure the pacemaker is secure and in harmony with the human body. Biocompatible materials must be used to construct the pacemaker's casing and the leads (wires) that attach to the heart. Additionally, encapsulation techniques are used to protect the electronic components from physiological fluids and corrosion over time, such as hermetic sealing or sophisticated polymer coatings. This encapsulation procedure is essential to guaranteeing the pacemaker's longterm functionality without endangering the patient or making them uncomfortable.

A well-known software provider with a focus on electronic design automation (EDA) solutions is Cadence. When creating integrated circuits (ICs), printed circuit boards, and other electronic systems, semiconductor manufacturers frequently utilize this programme. A variety of software tools are available from Cadence, including Cadence or CAD for PCB schematic capture and simulation, Cadence Virtuoso for IC design, and Cadence Allegro for PCB design. By using these tools, engineers and designers may construct and improve electronic designs and make sure they satisfy demands for performance, power, and manufacturability. The contemporary method of designing electronics includes cadence software. The development of sophisticated signal processing and algorithmic techniques is essential for pacemaker operation. Real-time electrical signal analysis of the heart is done by engineers using algorithms. These algorithms detect aberrant or excessively slow heart rhythms and signal the pacemaker to generate electrical impulses to speed up the heartbeat. Signal processing methods allow for the accurate identification of heart activity by filtering out noise and artefacts. The pacemaker's reactions are both efficient and secure because the algorithms are continuously improved to adapt to the patient's unique needs and condition. These approaches combine to create, improve, and maintain pacemakers, which are life-saving tools for people with bradycardia or cardiac arrhythmias. Pacemakers are carefully engineered to offer patients dependable and secure treatment alternatives for various cardiac diseases.

Fig -3: Block Diagram

L

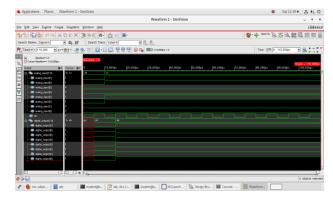

## **11. RESULT**

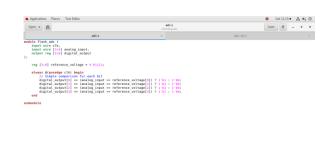

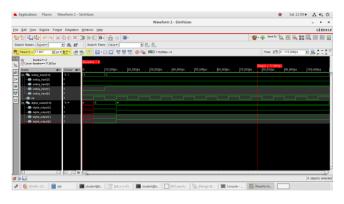

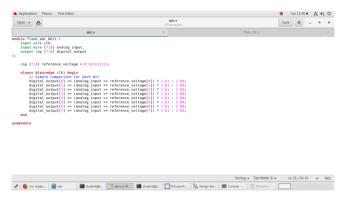

The development of a low-power 4-bit and 8-bit analog-todigital converter (ADC) for pacemakers represents a significant advancement in implantable medical device technology. By minimizing power consumption, this innovation directly addresses a critical concern in pacemaker design, ensuring prolonged battery life.

The efficient ADC implementation contributes to extended pacemaker lifespan, reducing the frequency of battery replacements and associated surgical interventions. This not only enhances patient convenience but also minimizes risks and costs associated with battery replacement procedures. The focus on low power in ADC design aligns with the imperative of maximizing energy efficiency in implantable devices, ultimately promoting the overall effectiveness and reliability of pacemakers in regulating cardiac rhythm.

| Open 👻 📇                                                                                                                                                    | *adc_tb.v    |           | Save ≡ - | . • × |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|----------|-------|

| adc.v                                                                                                                                                       |              | *adc_tb.v |          | ×     |

| timescale Ins / Ips                                                                                                                                         |              |           |          |       |

| <pre>dule testbench;<br/>reg [1:0] analog_input;<br/>wire [1:0] digital_output;</pre>                                                                       |              |           |          |       |

| <pre>// Instantiate the ADC module flash.adc uut (         -Clk(c(k),         .analog_input(analog_input),         .digital_output(digital_output) );</pre> |              |           |          |       |

| <pre>// Clock generation always begin     #5 clk = -clk; end</pre>                                                                                          |              |           |          |       |

| <pre>// Testbench stimulus initial begin     clk = 0;     analog_input = 4'b0000;</pre>                                                                     |              |           |          |       |

| #10 analog_input = 4'b0010; // Simulate an in                                                                                                               | nput voltage |           |          |       |

| // Add further simulation steps as needed                                                                                                                   |              |           |          |       |

| #100 Sfinish;<br>end                                                                                                                                        |              |           |          |       |

| deodule                                                                                                                                                     |              |           |          |       |

Fig -4: 4 bit ADC Testbench Verilog code

Fig -5: 4 bit ADC Compilation

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056 IRJET Volume: 10 Issue: 12 | Dec 2023 www.irjet.net p-ISSN: 2395-0072

Fig -7: 4 bit ADC Output

Fig -9: 8 bit ADC Verilog code

Fig -10: 8 bit ADC Compilation

Fig -11: 8 bit ADC Output

|                               |         |                             |                        | student@                                          | sns:syn       |             | -       |   | > |

|-------------------------------|---------|-----------------------------|------------------------|---------------------------------------------------|---------------|-------------|---------|---|---|

| File Ed                       | it View | Search                      | Terminal               | Help                                              |               |             |         |   |   |

| Instanc                       | e: /ADC |                             |                        |                                                   |               |             |         |   |   |

| Power U                       | nit: W  |                             |                        |                                                   |               |             |         |   |   |

| PDB Fra                       | mes: /s | tim#0/                      | frame#0                |                                                   |               |             |         |   |   |

|                               |         |                             |                        |                                                   |               |             |         | - |   |

| Cat                           | egory   |                             | Leakage                | Internal                                          | Switching     | Total       | Row     | 6 |   |

| m                             | emory   | 0.0                         | 0000e+00               | 0.00000e+00                                       | 0.00000e+00   | 0.00000e+00 | 0.00    | 5 |   |

| rea                           | ister   | 9.0                         | 2364e-07               | 8.61495e-05                                       | 6.68706e-06   | 9.37389e-05 | 70.99   | 6 |   |

| 23537                         | latch   | 0.0                         | 000e+00                | 0.00000e+00                                       | 0.00000e+00   | 0.00000e+00 | 0.00    | 6 |   |

|                               | logic   | 7.7                         | 5661e-07               | 1.90652e-05                                       | 1.14602e-05   | 3.13010e-05 | 23.719  | 6 |   |

|                               | bbox    | 0.0                         | 0000e+00               | 0.00000e+00                                       | 0.00000e+00   | 0.00000e+00 | 0.00    | 6 |   |

|                               | clock   | 0.0                         | 000e+00                | 0.00000e+00                                       | 7.00000e-06   | 7.00000e-06 | 5.309   | 6 |   |

|                               | pad     | 0.0                         | 000e+00                | 0.00000e+00                                       | 0.00000e+00   | 0.00000e+00 | 0.00    | 6 |   |

|                               | pm      | 0.0                         | 000e+00                | 0.00000e+00                                       | 0.00000e+00   | 0.00000e+00 | 0.009   | 6 |   |

|                               |         |                             |                        |                                                   |               |             |         |   |   |

| Sub                           | total   | 1.6                         | 7802e-06               | 1.05215e-04                                       | 2.51472e-05   | 1.32040e-04 | 100.009 | 6 |   |

| Perce                         | ntage   |                             | 1.27%                  | 79.68%                                            | 19.05%        | 100.00%     | 100.00  | 6 |   |

|                               |         |                             |                        |                                                   |               |             |         |   |   |

| Another<br>CURRENT<br>.1G, pe | RESOUR  | within<br>CES: R<br>G, phys | F {elapse<br>s curr: ( | nd will termin<br>ed: 157s, ST:<br>0.5G, phys pea | 18s, FG: 18s, | CPU: 6.3%}, |         |   |   |

Fig -12: Power Report Output of ADC

|                                  | student@sns:syn _ 🗖                                  | I X  |

|----------------------------------|------------------------------------------------------|------|

| File Edit View Search Te         | erminal Help                                         |      |

| : flow. Ignoring                 | frequency scaling.                                   |      |

| Warning: PWRA-0304 [Pwr          | Warn] -stim option is not applicable with vectorless | mode |

| : of power analy                 | vsis, ignored this option.                           |      |

| Info : PWRA-0002 Star            | ted 'vectorless' power computation.                  |      |

| Info : PWRA-0002 Fini            | shed power computation.                              |      |

| Info : PWRA-0007 [Pwr            | 'Info] Completed successfully.                       |      |

| : Info=6, Warn=2                 | 2, Error=0, Fatal=0                                  |      |

| Output file: counter po          | ower.rpt                                             |      |

| WARNING: This version o          | of the tool is 950 days old.                         |      |

| legacy genus:/> report           | area                                                 |      |

|                                  |                                                      |      |

| Generated by:                    | Genus(TM) Synthesis Solution 20.11-s111_1            |      |

| Generated on:                    | Dec 02 2023 03:58:11 pm                              |      |

| Module:                          | ADC                                                  |      |

| Technology library:              |                                                      |      |

|                                  | typical (balanced_tree)                              |      |

| Wireload mode:                   | enclosed                                             |      |

| Area mode:                       | timing library                                       |      |

|                                  |                                                      |      |

|                                  |                                                      |      |

| Instance Module Cell (           | Count Cell Area Net Area Total Area Wireload         |      |

|                                  |                                                      |      |

| counter<br>(D) = wireload is def | 49 319.412 0.000 319.412 <none> (D)</none>           |      |

|                                  |                                                      |      |

Fig -12: Power Report Generation using the Constraint File

# **12. CONCLUSIONS**

In the realm of Implantable Medical Devices (IMDs), achieving ultra-low-power capabilities is crucial for the successful implementation of signal processing algorithms. This necessity extends across various dimensions, requiring optimization at the levels of architecture, circuit design, and process selection. Each stage plays a pivotal role in determining the overall power efficiency of IMDs, which are often constrained by limited energy sources and the imperative to minimize the need for frequent interventions.

The proposed architecture emerges as a promising solution, providing a robust framework tailored to support implantable medical platforms with intelligent and dynamic power management. By addressing the multifaceted challenges of ultra-low-power requirements, this architecture goes beyond mere signal processing.

It integrates adaptive power management strategies, ensuring that the device operates with optimal energy efficiency throughout its lifecycle. Intelligent dynamic power management is particularly noteworthy as it allows the IMD to adapt its power consumption based on real-time demands, optimizing energy usage without compromising performance. This approach not only extends the lifespan of the device's battery but also minimizes the necessity for invasive procedures, offering a more patient-centric and sustainable solution. In essence, the proposed architecture exemplifies a holistic and forward-thinking approach to the development of IMDs. As a result, this architecture holds the potential to significantly advance the field of implantable medical technology, enhancing patient outcomes and contributing to the evolution of sophisticated, low-power medical devices.

## **13. FUTURE WORK**

Harnessing body energy for pacemaker devices is an innovative approach that relies on energy harvesting techniques to power these critical medical implants.

Potential sources of energy include the patient's heartbeat, blood flow within vessels, movement of body parts, and body temperature. By converting these physiological processes into electrical energy, pacemakers can be sustained without the need for frequent battery replacements.

To optimize the energy efficiency of the pacemaker circuit, reducing power consumption is paramount. This involves decreasing the chip size to 45 nm or 90 nm, a strategy that not only conserves space but also enhances the overall efficiency of the circuit. Smaller chip sizes enable a more energy-efficient operation, aligning with the goal of creating sustainable and long-lasting pacemaker devices.

The integration of energy harvesting and miniaturization technologies signifies a transformative shift in pacemaker design, making them more self-sufficient and attuned to the body's natural energy resources. This not only addresses the challenge of battery replacements but also opens avenues for developing next-generation implantable medical devices that seamlessly integrate with the body's physiological processes.

# REFERENCES

- V. Kakkar, "An Ultra Low Power System Architecture for Implantable Medical Devices, "in IEEE Access, vol. 7, pp. 111160-111167, 2019, doi: 10.1109/ACCESS.2018.2799422.

- [2] S. Ahmed and V. Kakkar, "An Electret-Based Angular Electrostatic Energy Harvester for Battery-Less Cardiac and Neural Implants," in IEEE Access, vol. 5, pp. 19631-19643, 2017, doi: 10.1109/ACCESS.2017.2739205.

- [3] Andreas Bahr, Matthias Schneider, Maria Avitha Francis, Hendrik M. Lehmann, Igor Barg, Anna-Sophia Buschhoff, Peer Wulff, Thomas Strunskus. Franz Faupel Epileptic "Seizure Detection on an Ultra-Low-Power Embedded RISC-V Processor Using a Convolutional Neural Network" Biosensors, 2021, vol 11.

- [4] P. Bikki, Y. Dhiraj and R. V. S. Nivas Kumar, "Implementation of a Dual-Chamber Pacemaker for Low-Power Applications," 2023 Fifth International Conference on Electrical, Computer and Communication Technologies (ICECCT), Erode, India, 2023, pp. 1-5, doi: 10.1109/ICECCT56650.2023.10179677.

- [5] Y. Chen, Y. Feng, S. Zhang, G. He, Y. Li, and D. Wang, "A novel noncoupling capacitor split capacitor array structure for high resolution SAR ADC," Mod. Phys. Lett. B 36(08), 2250001 (2022).

- [6] Y. Chen, Y. Liu, Y. Li, G. Wang and M. Chen, "An Energy-Efficient ASK Demodulator Robust to Power-Carrier-Interference for Inductive Power and Data Telemetry," in IEEE Transactions on Biomedical Circuits and

e-ISSN: 2395-0056 p-ISSN: 2395-0072

Systems, vol. 16, no. 1, pp. 108-118, Feb. 2022, doi: 10.1109/TBCAS.2022.3146559.

- I. Cretu et al., "Techniques to aid prediction of pacing dependence at 30 days in patients requiring pacemaker implantation after cardiac surgery," 2022 44th Annual International Conference of the IEEE Engineering in Medicine & Biology Society (EMBC), Glasgow, Scotland, United Kingdom, 2022, pp. 2647-2650, doi: 10.1109/EMBC48229.2022.9871616.

- [8] G. Di Patrizio Stanchieri, G. Battisti, A. De Marcellis, M. Faccio, E. Palange and T. G. Constandinou, "A New Multilevel Pulsed Modulation Technique for Low Power High Data Rate Optical Biotelemetry," 2021 IEEE Biomedical Circuits and Systems Conference (BioCAS), Berlin, Germany, 2021, pp. 1-5, doi: 10.1109/BioCAS49922.2021.9644996.N.

- [9] S. Doliwa, A. Erbslöh, K. Seidl and I. Iossifidis, "Development of an Analog Front-End for Brain-Computer Interfaces," 2022 17th Conference on Ph.D Research in Microelectronics and Electronics (PRIME), Villasimius, SU, Italy, 2022, pp. 309-312, doi: 10.1109/PRIME55000.2022.9816757.

- [10] F. Faisal, M. Zada, H. Yoo, I. B. Mabrouk, M. Chaker and T. Djerafi, "An Ultra-Miniaturized Antenna With Ultra-Wide Bandwidth for Future Cardiac Leadless Pacemaker," in IEEE Transactions on Antennas and Propagation, vol. 70, no. 7, pp. 5923-5928, July 2022, doi: 10.1109/TAP.2022.3161513.